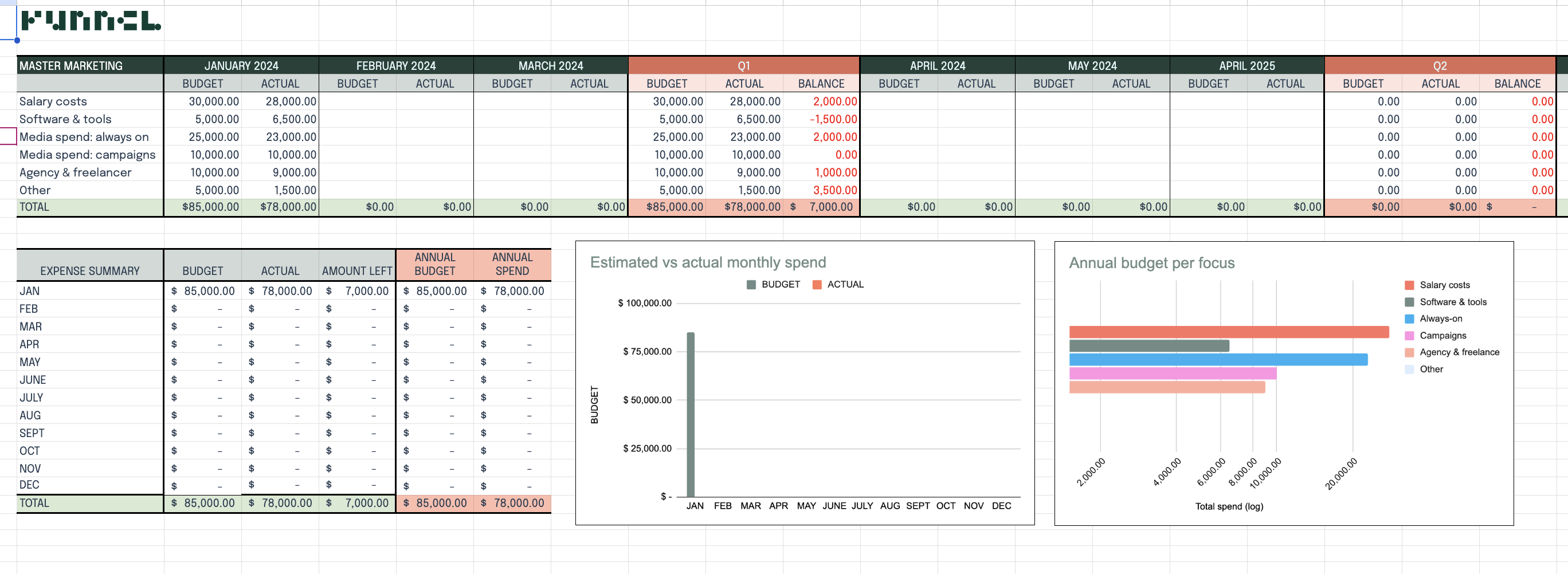

🔥PCIe Gen4 / Gen5 为何频频翻车?

一次讲透:通道预算 × EQ × PI 联合仿真的“真实工程逻辑”

🎯写给: 正在做 Gen4 / Gen5,却总感觉“哪里不对劲”的你

🚗关键词:PCIe Gen4 / Gen5、Channel Budget、EQ、PI、Eye Diagram、联合仿真

一、先泼一盆冷水:

PCIe Gen5 的问题,90% 不在“线”,而在“系统”

很多人第一次上 Gen4 / Gen5,都会经历同一个阶段:

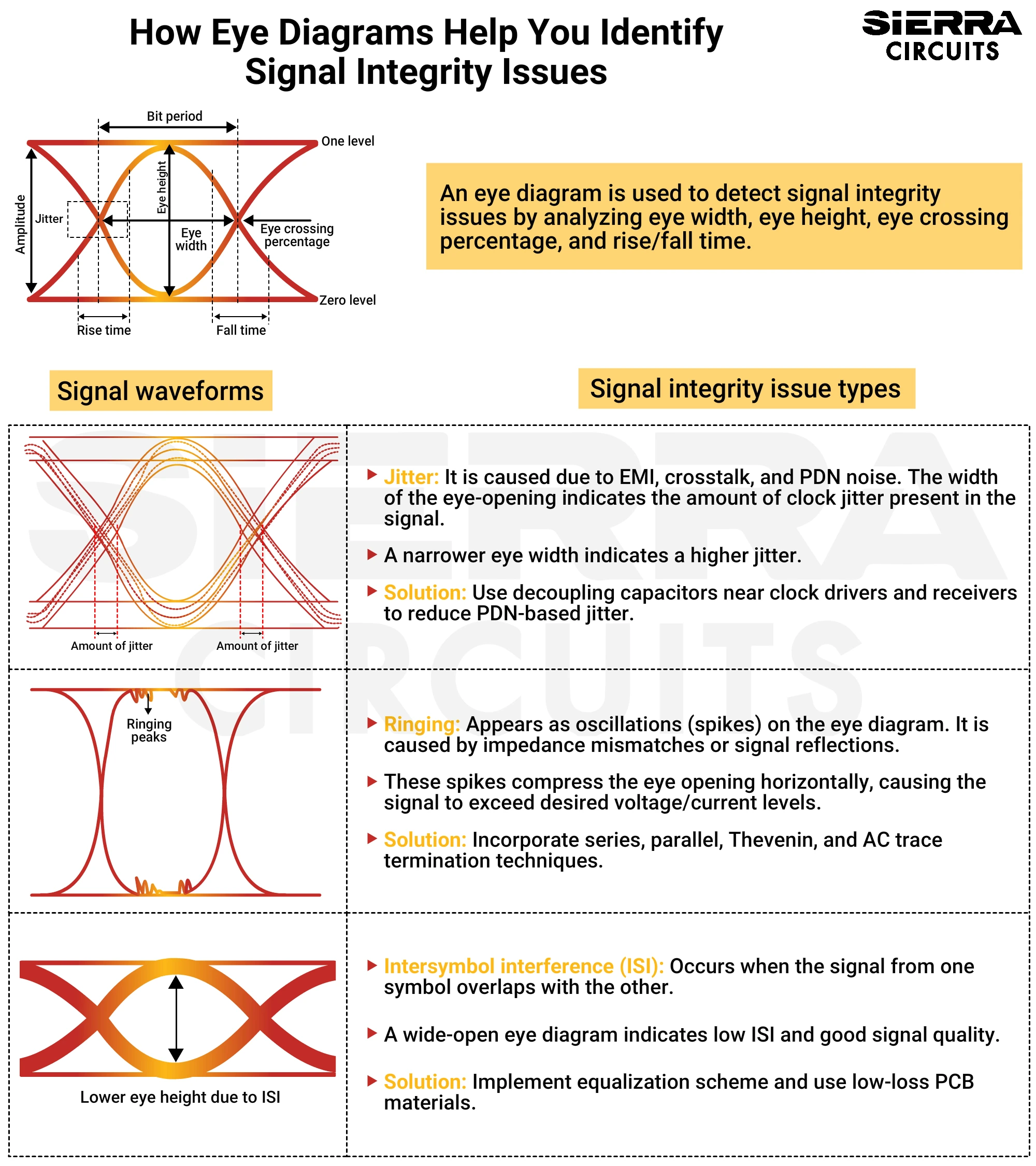

✔ 插损算过 ✔ SI 仿真跑过 ✔ 规则全按 Guide 来 ❌ 上板后眼图一塌糊涂

问题真不是你不认真,而是——

Gen5 已经不是“高速布线问题”, 而是“系统协同设计问题”。

二、什么叫“通道预算”?别再只盯着插损了 🚨

1️⃣ 通道预算 ≠ 一条插损曲线

在真实工程里,通道至少拆成 4 块:

L

o

s

s

t

o

t

a

l

(

f

)

=

L

o

s

s

t

r

a

c

e

(

f

)

+

L

o

s

s

v

i

a

(

f

)

+

L

o

s

s

c

o

n

n

e

c

t

o

r

(

f

)

+

L

o

s

s

p

a

c

k

a

g

e

(

f

)

Loss_{total}(f)= Loss_{trace}(f)+ Loss_{via}(f)+ Loss_{connector}(f)+ Loss_{package}(f)

Losstotal(f)=Losstrace(f)+Lossvia(f)+Lossconnector(f)+Losspackage(f)

🎯 工程视角重点:

- Gen4 看 8 GHz

- Gen5 看 16 GHz

- 不是“某一点过没过”,而是整段频谱是否可 EQ

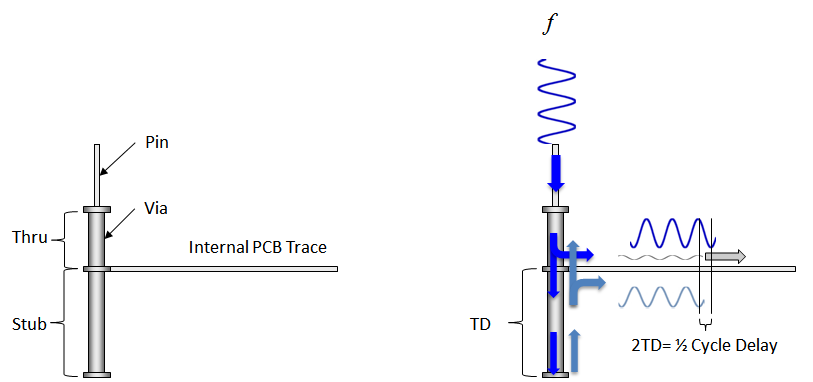

2️⃣ Via:最容易被低估的“慢性毒药”

4×624.png&pos_id=img-t5BOTeff-1767451078425)

很多板子是这样死的:

线不长 材料不差 但过孔 Stub 太长

过孔谐振频率近似为:

f

r

e

s

≈

c

4

L

s

t

u

b

ε

r

f_{res}\\approx \\frac{c}{4L_{stub}\\sqrt{\\varepsilon_r}}

fres≈4Lstubεr

c

🎯 经验结论(真踩过坑):

| Gen4 | Stub < 0.3 mm |

| Gen5 | 必须 Back-drill |

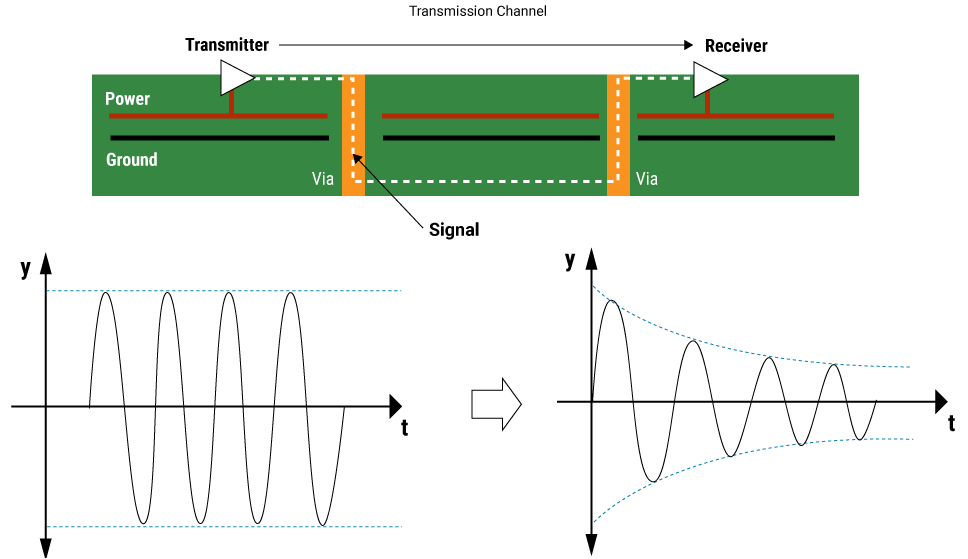

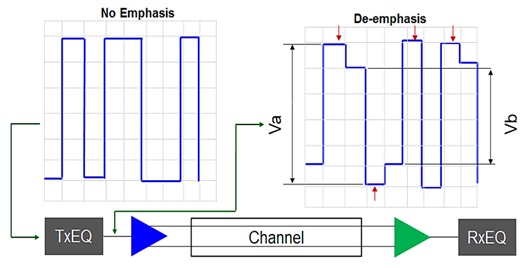

三、EQ 不是“解药”,更像“兴奋剂”🔥

1️⃣ EQ 本质:不是修复,而是补偿

EQ 想干的事只有一句话:

H

c

h

a

n

n

e

l

(

f

)

⋅

H

E

Q

(

f

)

≈

1

H_{channel}(f)\\cdot H_{EQ}(f)\\approx1

Hchannel(f)⋅HEQ(f)≈1

但请注意:

EQ 只能补“线性损耗”, 不能消灭噪声。

2️⃣ 工程真相:EQ 会放大“你不想放大的东西”

⚠️ EQ 的副作用包括:

- 高频噪声被拉高

- 抖动被重新分布

- 电源噪声 → 直接进眼图

🎯 所以才有这个反直觉结论:

插损越大, 系统对 PI 的要求反而越苛刻

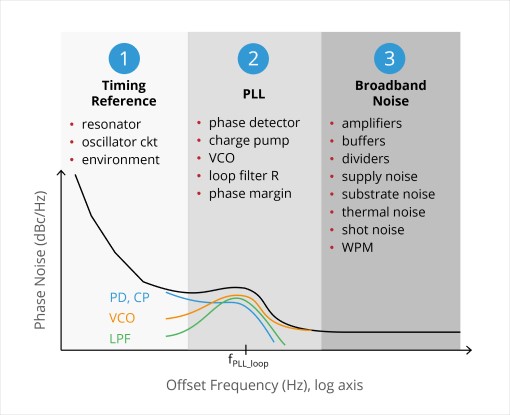

四、为什么 Gen5 一定要把 PI 拉进来?🚗

1️⃣ 眼图不好,不一定是 SI 的锅

在 Gen5 时代,下面这条链路非常真实:

PDN Noise

→ PLL Phase Noise

→ TX Jitter

→ Eye Closure

2️⃣ 抖动不是“一种”,而是叠加

σ

t

o

t

a

l

=

σ

R

J

2

+

σ

D

J

2

+

σ

P

J

2

\\sigma_{total}= \\sqrt{ \\sigma_{RJ}^2+ \\sigma_{DJ}^2+ \\sigma_{PJ}^2 }

σtotal=σRJ2+σDJ2+σPJ2

其中:

-

σ

P

J

\\sigma_{PJ}

σPJ:电源相关抖动 - 在 Gen5 中占比明显上升

🎯 工程现象你一定见过:

SI 仿真完美 PDN 没分析 实测 Eye 完蛋

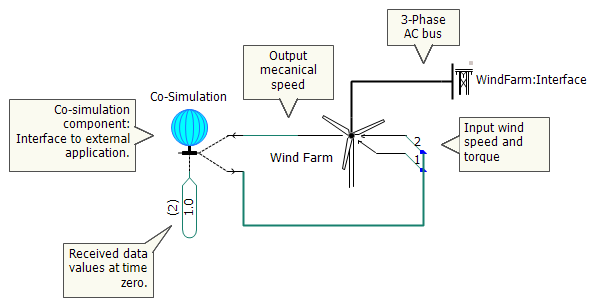

五、真正靠谱的流程:

通道 × EQ × PI 联合仿真(工程版)

✅ Step 1:通道先别“太烂”

- 插损留余量

- Via / Connector 优先处理

- 不把希望压在 EQ 上

✅ Step 2:带 EQ 的 SI 才有意义

- IBIS-AMI

- 扫 Preset / CTLE / DFE

- 找 稳定区间,而不是极限值

✅ Step 3:把 PDN 拉进来

目标阻抗不是口号:

Z

t

a

r

g

e

t

=

Δ

V

Δ

I

Z_{target}= \\frac{\\Delta V}{\\Delta I}

Ztarget=ΔIΔV

重点看:

- TX / RX 供电阻抗

- 抖动是否随 PDN 波动

✅ Step 4:只看“系统 Eye”

🎯 最终判断标准只有一句话:

最差 PVT + 噪声条件下, BER 能不能稳住

六、结尾一句“人话总结”

PCIe Gen4 / Gen5 的难点, 从来不是你会不会算插损, 而是你有没有把它当“系统”在设计。

- 通道预算 ≠ 插损表

- EQ ≠ 万能补丁

- PI ≠ 事后修补

🎯 联合仿真不是进阶玩法,而是 Gen5 的生存底线。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册