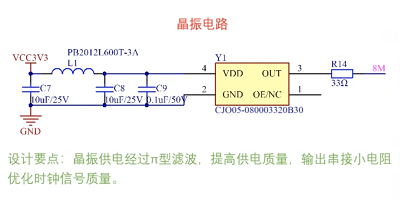

这个电路是一个带 π 型电源滤波和输出阻抗匹配的有源晶振时钟电路,核心功能是为嵌入式系统(如 MCU、FPGA)提供低噪声、高稳定性的时钟信号,下面从元件作用、工作原理、设计要点展开分析:

一、关键元件作用拆解

| L1(PB2012L600T-3A) | π 型滤波的电感,与 C6、C8、C9电容组成低通滤波网络,抑制 3.3V 电源的高频噪声,为晶振提供纯净的供电。 |

| C6(100nF/25V)、C8(100nF/25V)、C9(100nF/25V) | π 型滤波的电容:- C6(输入侧):滤除电源的高频噪声,减少从 VCC3V3 引入的干扰;- C8+C9(输出侧):进一步滤除低频纹波和高频毛刺,双重净化晶振的供电电源。 |

| CJO05-080003320B0(有源晶振) | 核心时钟源,内部集成振荡电路和温度补偿,输出稳定的 8MHz 时钟信号(型号中 “08000” 对应 8MHz);OE/NC 引脚接地,确保晶振持续使能输出。 |

| R14(33Ω) | 输出串联匹配电阻,用于时钟信号的阻抗匹配,减少高速信号传输时的反射、振铃和过冲,优化时钟信号质量,降低抖动。 |

二、核心工作原理

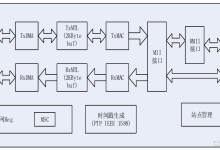

该电路通过 “电源净化→时钟生成→信号匹配” 三步实现稳定时钟输出:

三、设计要点解读

π 型滤波的必要性有源晶振对电源噪声极其敏感,电源上的纹波或毛刺会直接引入时钟抖动,导致系统时序错误(如 MCU 指令执行异常)。π 型滤波由电感和电容组成,能同时抑制差模和共模噪声,是晶振电源滤波的经典方案。

串联电阻 R14 的匹配逻辑时钟信号是高速数字信号,传输线的阻抗不匹配会引发信号反射,产生振铃和过冲,降低信号质量。33Ω 是典型的匹配电阻值,与常见传输线的特征阻抗(50Ω)接近,可有效减少反射,优化时钟信号的完整性。

布局优化

- 滤波元件(L1、C6、C8、C9)必须紧贴晶振的 VDD 引脚放置,缩短电源回路走线,减少寄生电感,提升滤波效果。

- 晶振和 R14 应 紧贴负载(如 MCU 的时钟输入引脚)放置,缩短时钟线长度,减少信号衰减和外部干扰。

有源晶振的优势有源晶振内部集成了振荡电路和温度补偿,比无源晶振具有更高的频率稳定性和更低的抖动,适合对时钟精度要求高的场景(如通信、数据采集系统)。

四、典型应用场景

该电路广泛用于嵌入式系统的时钟源设计,例如:

- MCU/FPGA 的系统时钟输入;

- 通信模块(如 Wi-Fi、蓝牙)的时钟源;

- 高精度数据采集设备的同步时钟。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册