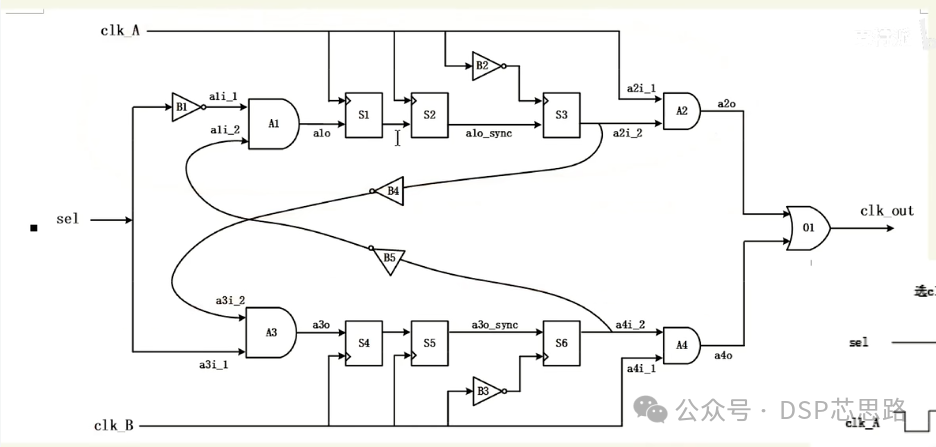

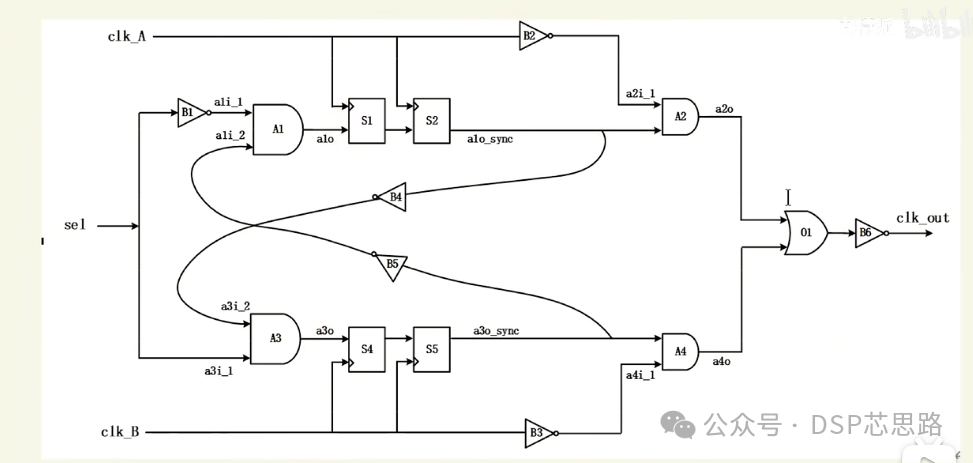

结构1

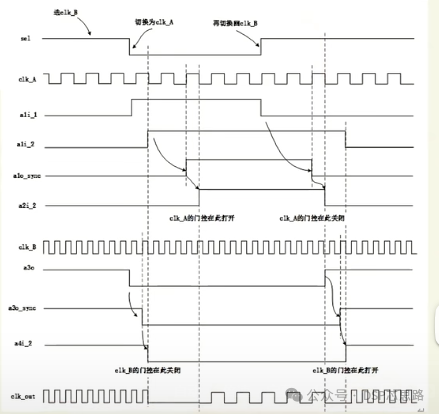

首先CLK_A和CLK_B是异步时钟,sel信号和CLKA\\CLKB也是异步关系。所以需要将sel信号的组合逻辑同步到CLK_A和CLK_B的时钟域下,所以出现了上图S1\\S2\\S3\\S4四个异步对接打拍的两级寄存器。图中B2和S3以及B3和S6的结构的目的是将同步后的信号变成下降沿采样。这么做可以防止出现毛刺。同时A2和A4作为时钟开关电路,将CLK_A和CLK_B输出到clk_out。当进行时钟切换时,sel信号由0变到1,经过两级同步,同时经过一级负沿采样才传到A2将时钟CLK_A关闭,这是输出时钟也是关闭的。S3的输出需要经过下面时钟的两级同步,再经过下面时钟的负沿采样才能传到A4将CLK_B打开。

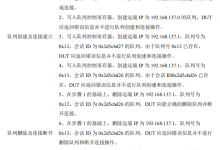

初始状态默认S1\\S2\\S3的复位值为1,S4\\S5\\S6的复位值为0。默认输出CLK_A。当需要默认输出CLK_B时,将S1\\S2\\S3的复位值为0,S4\\S5\\S6的复位值为1。

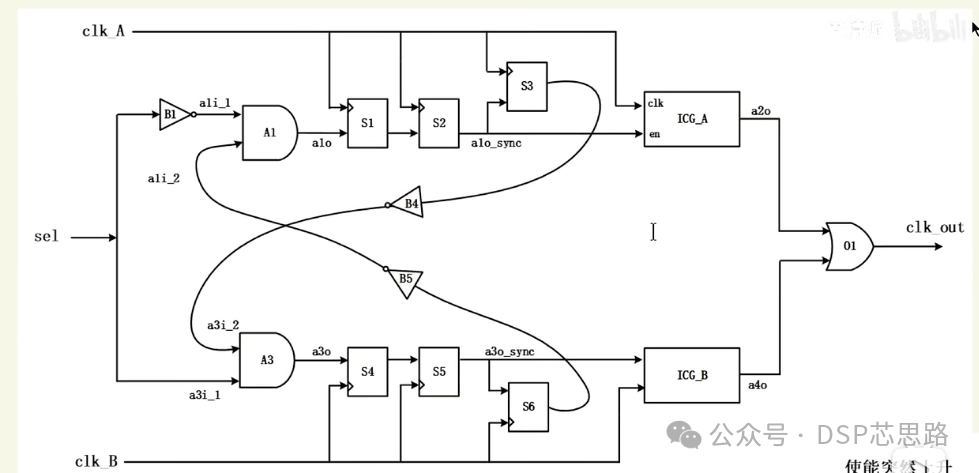

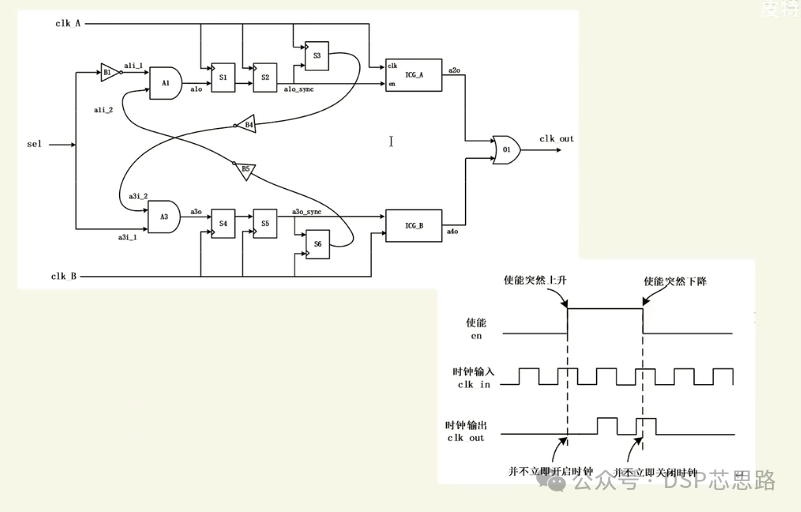

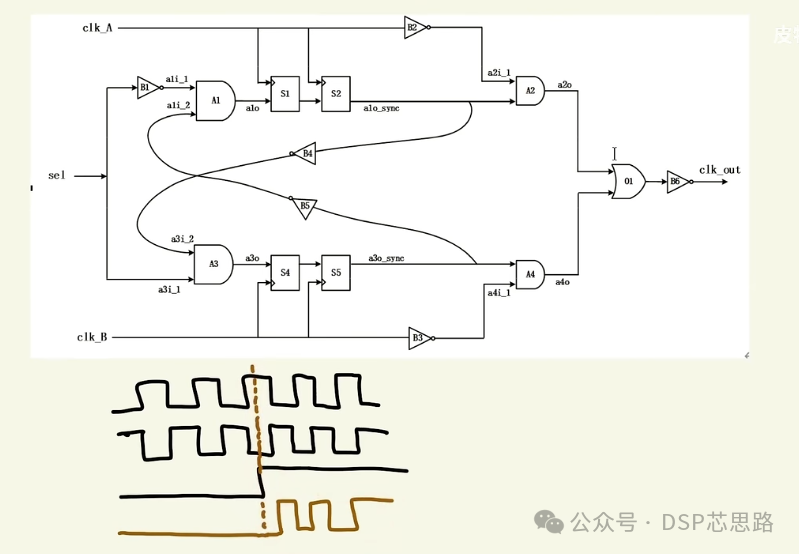

2、结构2

结构2和结构1的区别在于将与门换成了时钟门控单元ICG了,同时将S3和S6换成了正沿采样,而且时钟门控使能信号也是直接由同步后的信号产生。因为ICG可以保证时钟不突变,且采样信号是在下降沿采样。所以S3和S6可以换成上升沿采样。此时S3和S6是不是多余了呢?答案是否定的,因为ICG有半周期延迟功能。假如从S2的输出直接街道下面来,如果CLK_B是个高频时钟而CLK_A是个低频时钟,则会出现上面的时钟ICG_A还没关掉,下面的时钟ICG_B已经打开了,导致输出时钟出现错误。而再打一拍的目的就是保证现有的时钟已经关闭了,而新时钟还未打开。这种结果还有个好处,避免了时钟树上出现组合逻辑门。

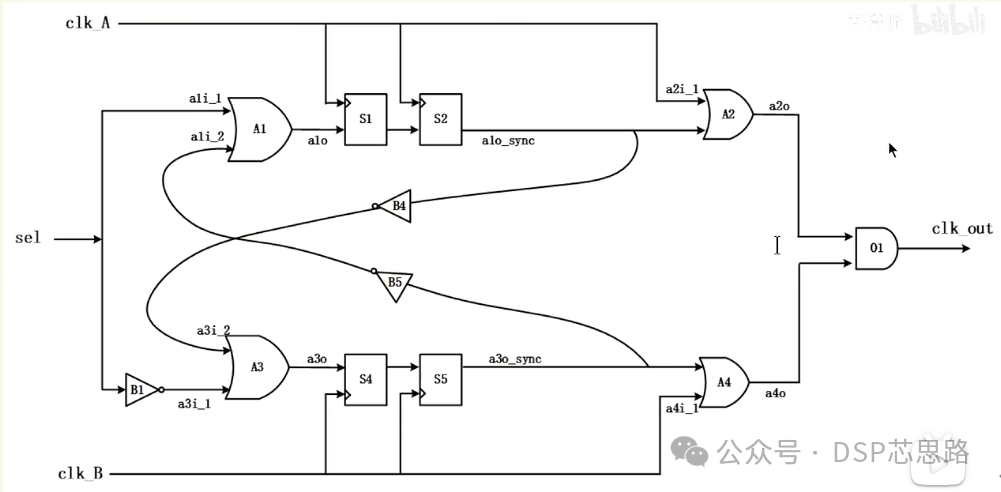

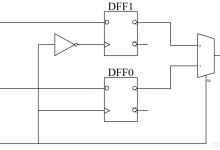

3、结构3

结构3和前面两种方案的最大区别是少了一级触发器,同时时钟是先取反饭后再经过与门。核心去毛刺的原理就是利用了时钟取反这个关键操作,保证sel信号和取反后的时钟做逻辑。时钟也不会有毛刺。这个方案有个好处是可以节省掉时钟切换的时间。节省切换前时钟的半个周期。但是这种方案存在问题就是当B2和B3延时较大或者布线延时较长时,还是可能出现毛刺。必须保证从CLK_A→S2的延时大于CLK_A→B2。

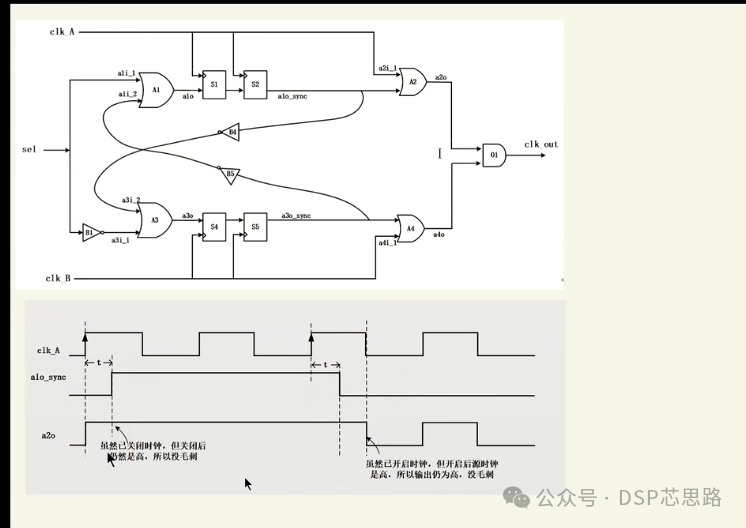

4、结构4

结构4和前面3个机构的最大区别是将原来的与门换成了或门,原来的或门换成了与门。这种结果时钟通过的条件和与门的刚好相反。sel信号为1时是将CLK_A关掉,sel信号为0时是将CLK_A打开。由于时钟都是上升沿采样,且门控逻辑门是或门,这是不产生毛刺的主要原因。这种结构有个不好的点是时钟数上出现了组合逻辑门。

总结:

1、四种结构中,结构3可能存在风险。

2、结构1和结构4存在的问题是时钟树上出现了组合逻辑门,时序约束时需要将使能信号声明为非时钟。

3、结构1和结构2的缺点是,切换的时间比结构3和结构4慢了原时钟的半拍。

4、结构4滤毛刺原理比较占优,同时消耗资源最少。

5、结构2时序约束最简单。时钟路径上没有特殊的单元。都是时钟单元。

6、综合考虑优选结构2。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册