章节导论

硬件描述语言(HDL)的高效开发离不开适配的工具链支撑,VS Code 作为轻量且可高度定制的代码编辑器,通过安装专用 HDL 插件可快速搭建低成本、高效率的 HDL 开发环境。本章聚焦 VS Code 下 HDL 开发环境的核心配置流程,重点讲解关键插件(Digital IDE、Verilog-HDL-Format)的安装、核心功能与使用规范,同时梳理环境配置中的前提条件和常见问题,帮助开发者通过插件赋能,解决 HDL 开发中语法纠错、代码复用、仿真调试等效率痛点,实现 Verilog/SV/VHDL 代码的标准化、高效化开发。

3.1 环境搭建前提条件

搭建 VS Code HDL 开发环境需先完成底层工具部署(如: Icarus Verilog),确保插件功能可正常调用:

- 安装 Icarus Verilog:作为基础的 Verilog 编译、仿真工具,是 Digital IDE 等插件实现语法诊断、快速仿真的核心依赖

- 【Icarus Verilog 安装教程参考第二章】;

- 官网下载地址:https://bleyer.org/icarus/

- 官网下载地址:https://code.visualstudio.com/Download

- 配置环境变量:将 Icarus Verilog 的安装路径添加至系统环境变量,确保 VS Code 插件可全局调用 iverilog 等命令。

3.2 VS Code 核心插件安装

3.2.1 安装插件的主要目的:提高开发效率

- 语法高亮

- 代码补全

- 实时纠错

- 一键启动【编译+仿真】

- 代码格式化

- 定义跳转

- 一键例化等

3.2.2 插件安装通用流程

- 打开 VS Code,进入左侧 “扩展” 面板(快捷键 Ctrl+Shift+X);

- 在搜索框输入插件名称,点击 “安装” 按钮;

- 插件安装完成后重启 VS Code,使功能生效。

3.2.3 核心插件列表

1. Digital IDE

- Digital IDE 官方网址:https://nc-ai.cn/article/cxnqr517/

- 安装:在 Vscode 插件商店中搜索 “Digital IDE” ,点击下载即可。

- 功能介绍:

- 语言高亮【安装插件就可用】

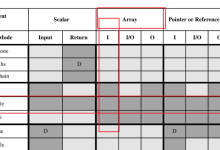

- 支持高亮的语法如下图所示:

- 支持高亮的语法如下图所示:

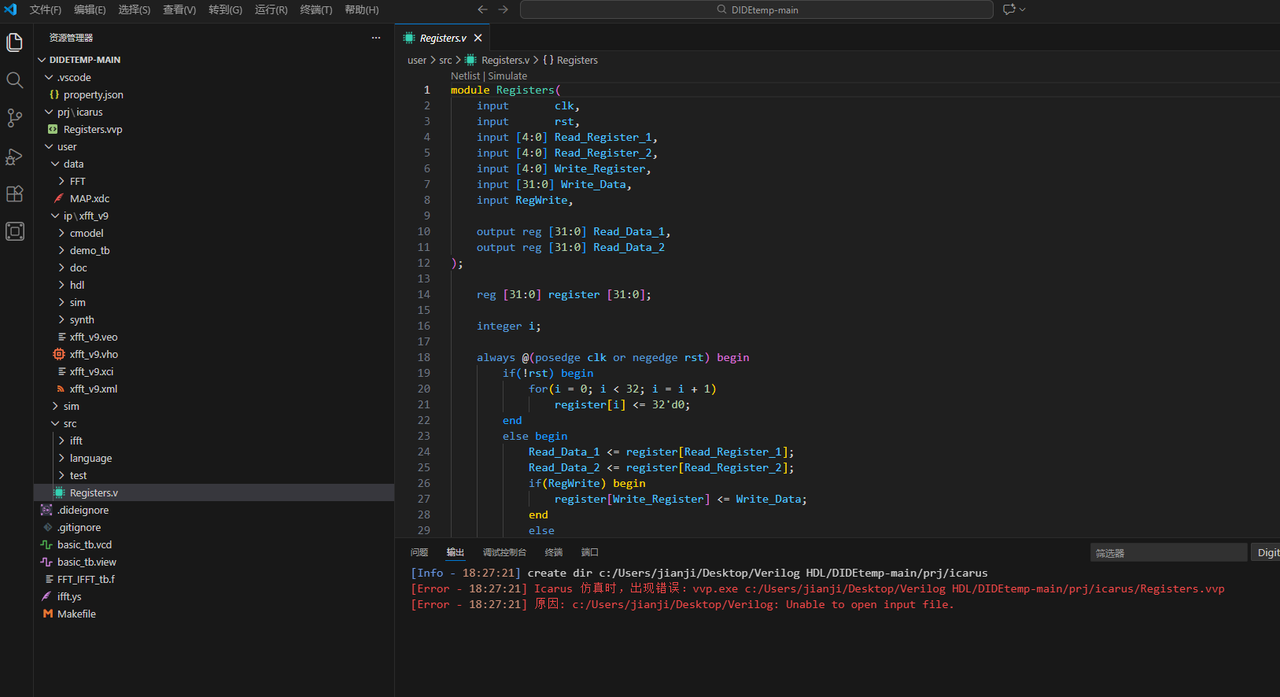

- 语法诊断【需要配置之后才可用】:语法诊断可以在开发中提前帮助开发者了解到代码中隐藏的语法错误,在编译或者运行前提前规避部分错误,提高开发效率

- 保存文件后,才会检查语法错误,有部分语法错误无法检测

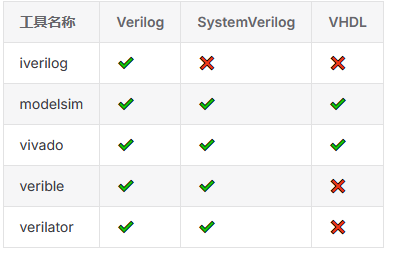

- 支持的诊断工具如下图所示:

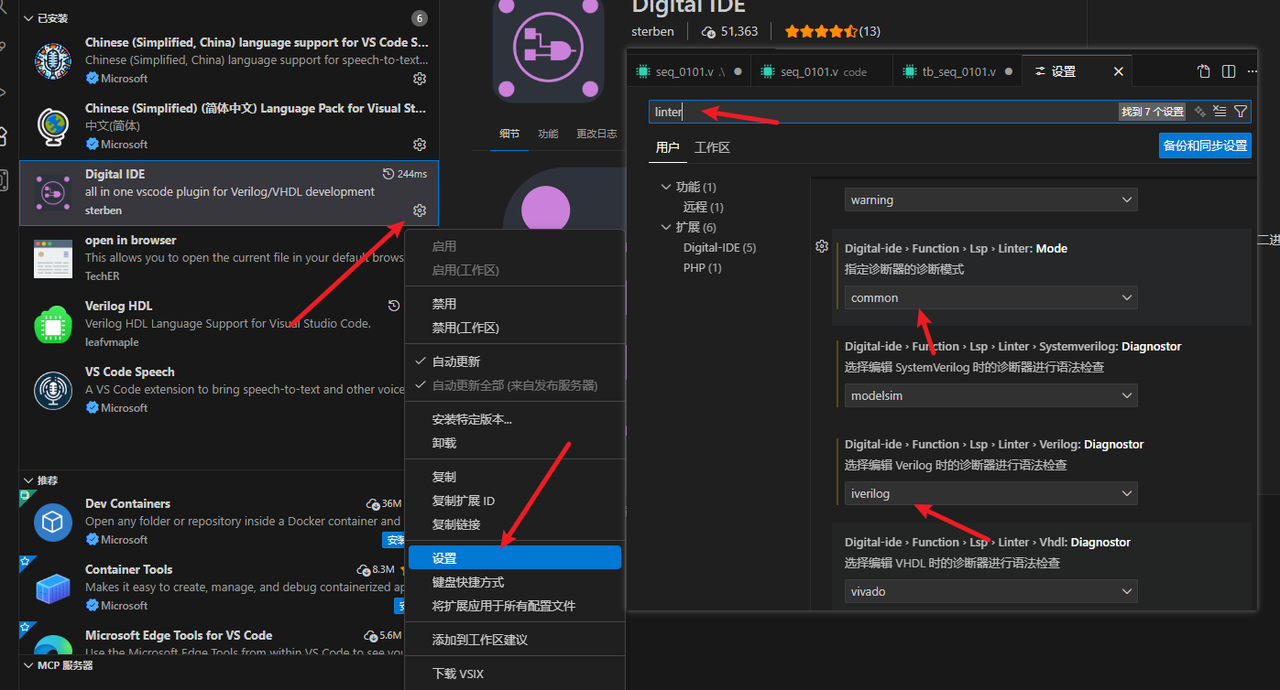

- 更换诊断器和诊断级别和诊断模式

- 修改配置中搜 linter 如下图

- 诊断级别

- error: 只显示错误

- warning: 显示错误和警告

- 诊断模式

- Full: 将所有设计源直接进行诊断,并报错,无论文件是否打开。

- Common: 单文件关闭时,对应报错去除,打开哪个文件就对哪个文件进行诊断。

- Shutdown: 全局关闭,即整个工程都不进行工程报错。(专心code)

- 诊断器【依赖诊断器的环境变量】

- iverilog:只支持verilog 语法检测

- modelsim:支持 verilog、SV、VHDL 语法检测

- vivado(xvlog):支持 verilog、SV、VHDL 语法检测

- verible:支持 verilog、SV 语法检测,不支持 VHDL 语法检测

- verilator:支持 verilog、SV 语法检测,不支持 VHDL 语法检测

- 修改配置中搜 linter 如下图

- 悬停提示【安装插件就可用】:把鼠标光标移动到一个变量上时,IDE 会负责将这个变量的上下文信息显示在光标的旁边

- 自动补全【安装插件就可用】

- 代码片段自动补全

- 关键词自动补全(关键词,系统函数,宏)

- 自动例化

- 原语例化

- 定义跳转 【安装插件就可用】:允许用户快速在编辑器中跳转到对应变量的定义的位置上,按Ctrl+鼠标左键点击

- 代码格式化【安装插件就可用】:选中需要格式化的代码,按快捷键 shift + alt + f

- 重启vs code

- 语言高亮【安装插件就可用】

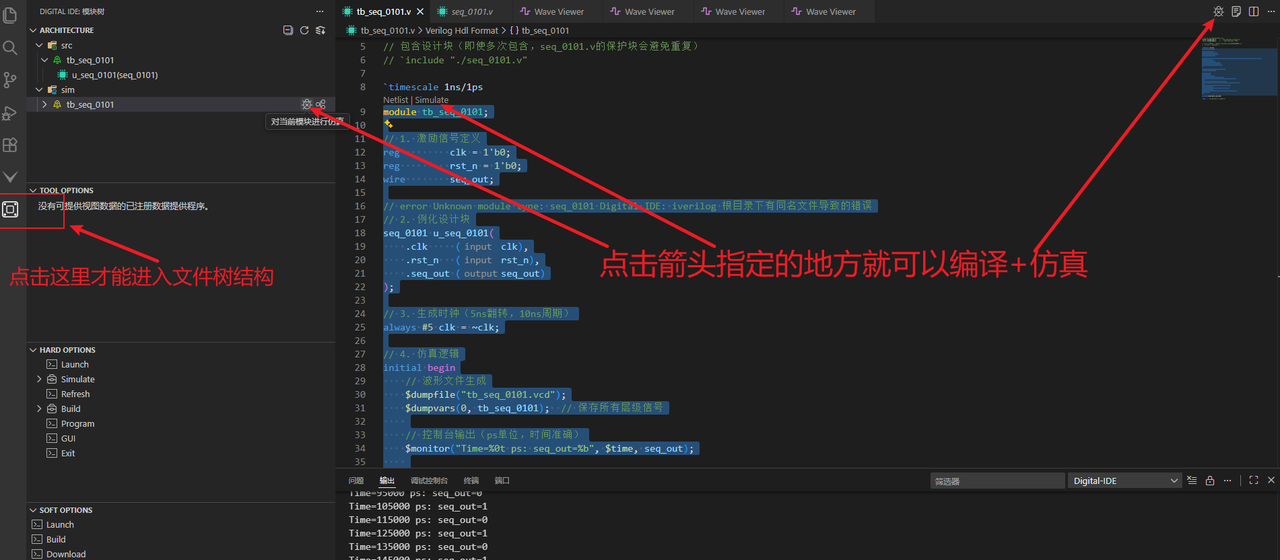

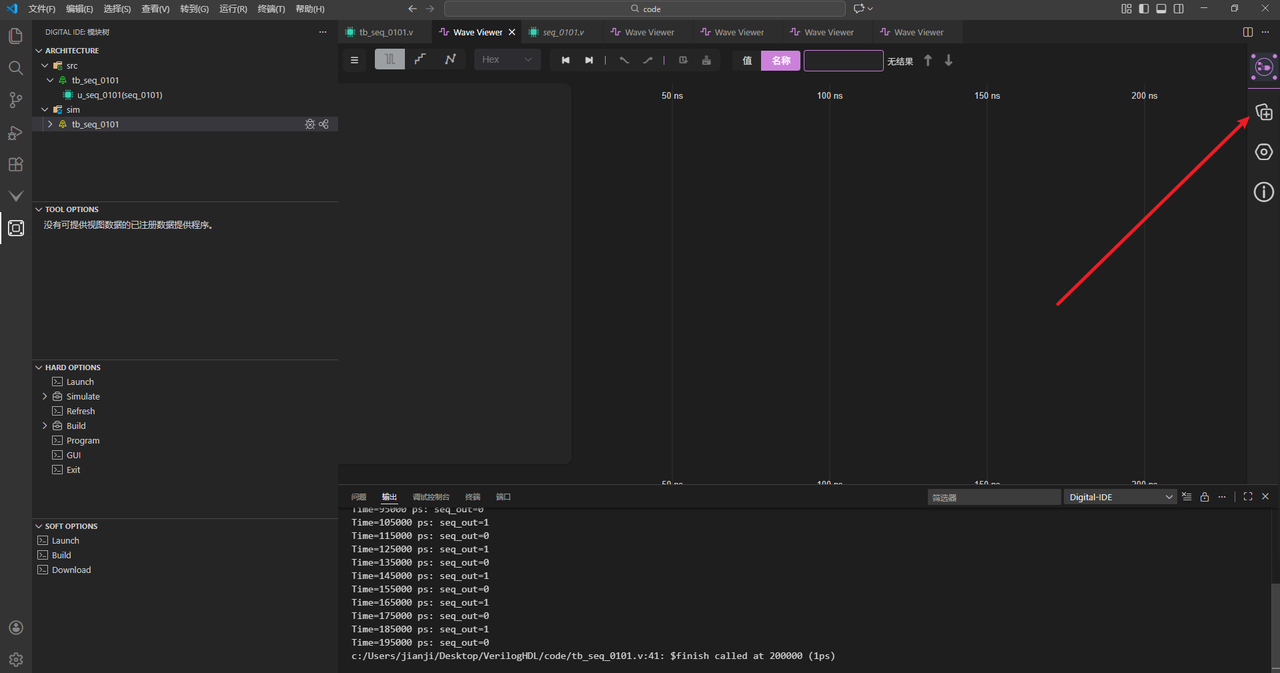

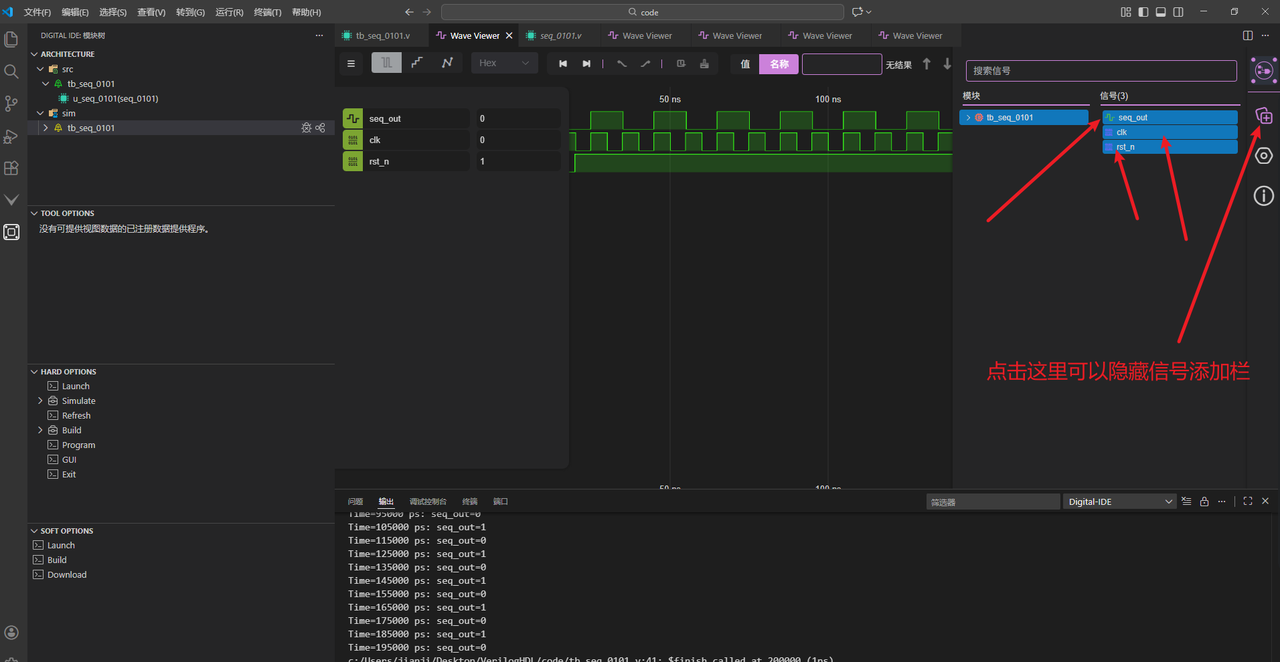

- 快速仿真【依赖诊断器(例如:Icarus Verilog) 的环境变量】

Digital IDE 对 include做了专门的设计,激励块无论写不写 include 都能正常仿真,但我们强烈不建议写include,include本身的设计会导致更高的复杂度,导致运行的不稳定性

- 添加信号生成波形

- 插件支持的功能如下:

- 官方网址:https://1391074994.github.io/Verilog-Hdl-Format/#/./README

- 代码格式化: 自动对齐 Verilog 代码的变量、逗号和括号,使代码更易读。

- 文件树显示: 以树状结构清晰地展示 Verilog/VHDL/SystemVerilog 文件的层次关系,方便代码导航。

- 一键例化【主要用到这个功能】: 快速生成 Verilog 模块例化代码,并自动复制到剪贴板,告别繁琐的手动编写。

- 🔵 【一键例化】 命令: Convert_instance 快捷键: 无

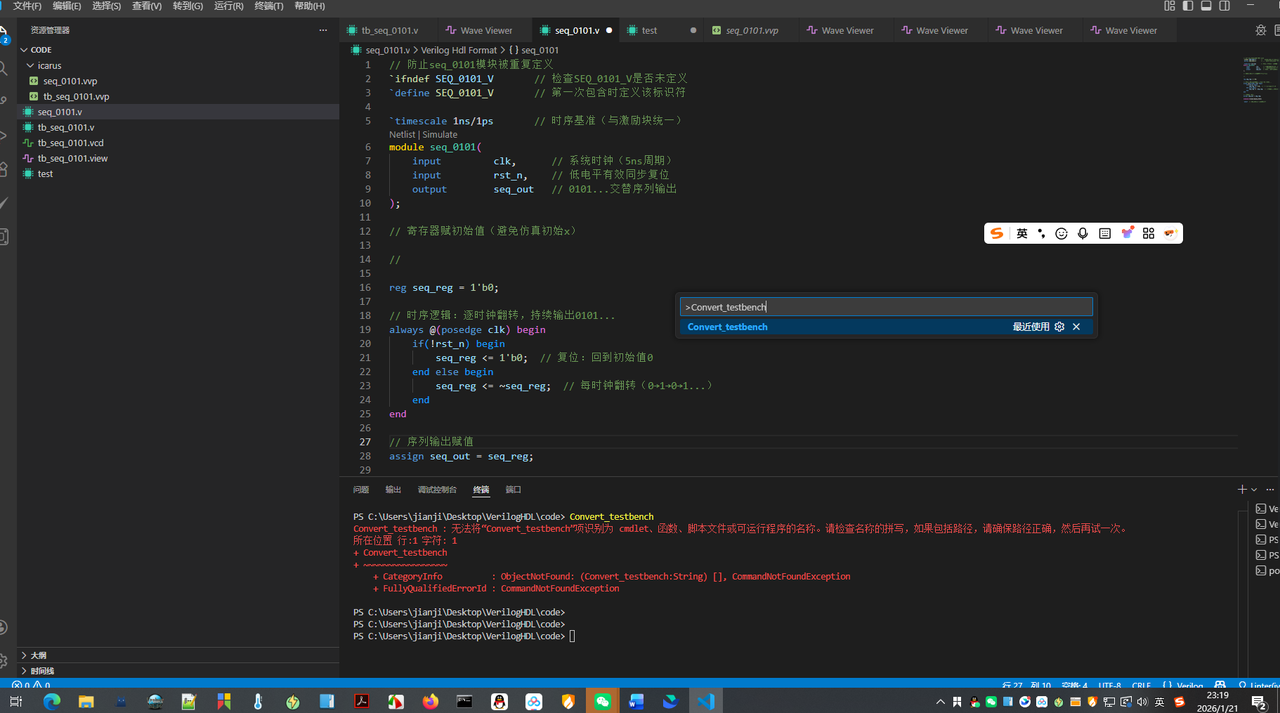

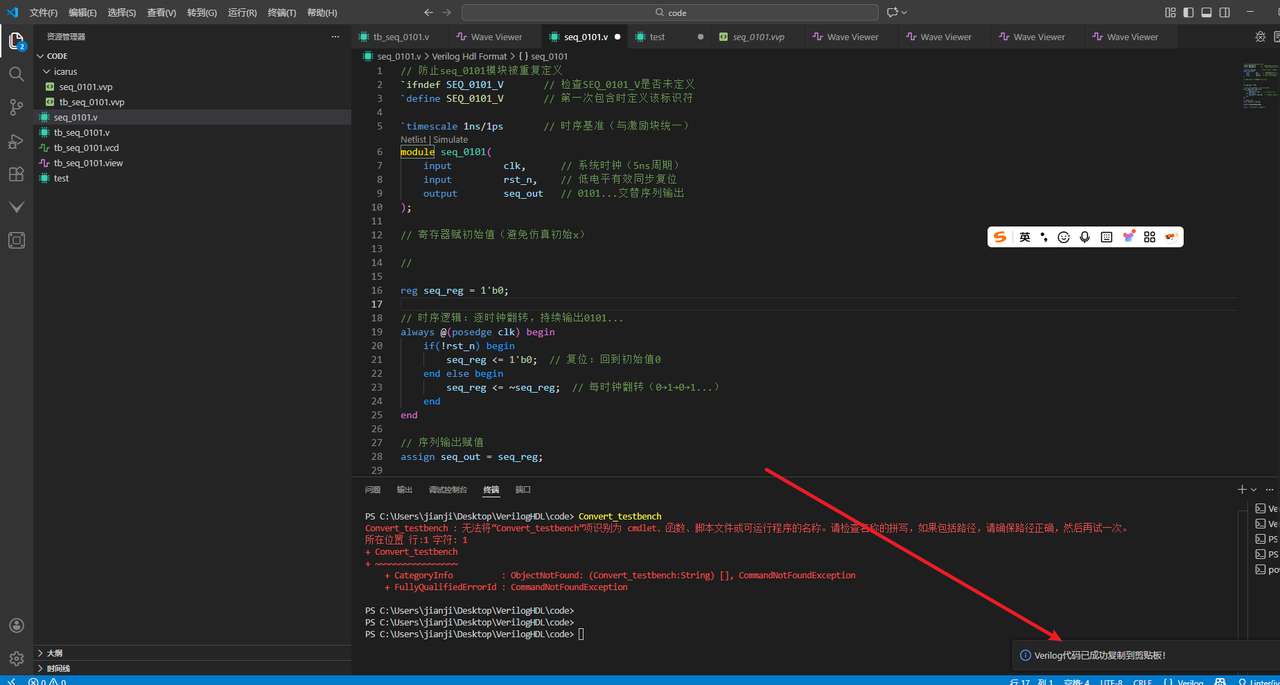

- 🔵 【一键 TB】 命令: Convert_testbench 快捷键: 无,生成的代码自动复制在剪切板【只能生成简单的 激励块代码,细节需要优化】

- 按 Ctrl + Shift + P 输入 Convert_testbench

- 自动生成的基础激励块(基础测试台)代码复制成功提示

- 语法高亮: 支持 ucf, xdc, do, tcl, Verilog, SystemVerilog, VHDL 和高云 .cst 语法高亮显示,提升代码可读性。

- 语法跳转: 快速跳转到模块定义、引脚定义和变量定义,提高代码阅读和调试效率 (集成 CTAGS)。

- 代码补全: 提供智能的 Verilog 代码补全建议,减少代码输入量。

- 定义悬停: 鼠标悬停在变量或模块名上即可查看其定义信息 (集成 CTAGS)。

- 语法检查: 使用 xvlog 进行 Verilog 语法错误检查,及早发现并修复潜在问题。

- VIVADO 联合仿真: 简化在 VSCode 中进行 VIVADO 联合仿真的流程 (Modelsim/QuestaSim)。

- VIVADO 程序备份和自动下载: 备份 VIVADO 工程的 bit 文件,并提供自动下载脚本,保障项目安全。

- Vivado 仿真文件快速转换: 转换 Vivado 仿真文件格式,方便不同工具之间的切换。

- FTP 功能: 方便地将 bit 文件上传到 FTP 服务器,实现远程部署。

- UCF 转 XDC 文件: 将 UCF 文件转换为 XDC 文件,方便进行约束文件的迁移。

- 数字递增/递减: 快速递增或递减选中的数字,提高编辑效率。

- 颜色主题: 提供自定义的 Verilog 颜色主题 (“jiang percy verilog themes”),个性化你的开发环境。

3.3 常见问题

原因:根目录下有同名文件导致的错误

3.4 附件

3.4.1 设计块代码

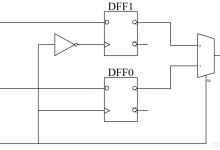

// 防止seq_0101模块被重复定义

`ifndef SEQ_0101_V // 检查SEQ_0101_V是否未定义

`define SEQ_0101_V // 第一次包含时定义该标识符

`timescale 1ns/1ps // 时序基准(与激励块统一)

module seq_0101(

input clk, // 系统时钟(5ns周期)

input rst_n, // 低电平有效同步复位

output seq_out // 0101…交替序列输出

);

// 寄存器赋初始值(避免仿真初始x)

//

reg seq_reg = 1'b0;

// 时序逻辑:逐时钟翻转,持续输出0101…

always @(posedge clk) begin

if(!rst_n) begin

seq_reg <= 1'b0; // 复位:回到初始值0

end else begin

seq_reg <= ~seq_reg; // 每时钟翻转(0→1→0→1…)

end

end

// 序列输出赋值

assign seq_out = seq_reg;

endmodule

`endif // SEQ_0101_V 保护块结束

3.4.2 激励块代码

// 防止tb_seq_0101模块被重复定义

`ifndef TB_SEQ_0101_V // 检查TB_SEQ_0101_V是否未定义

`define TB_SEQ_0101_V // 第一次包含时定义该标识符

// 包含设计块(即使多次包含,seq_0101.v的保护块会避免重复)

// `include "./seq_0101.v"

`timescale 1ns/1ps

module tb_seq_0101;

// 1. 激励信号定义

reg clk = 1'b0;

reg rst_n = 1'b0;

wire seq_out;

// error Unknown module type: seq_0101 Digital IDE: iverilog 根目录下有同名文件导致的错误

// 2. 例化设计块

seq_0101 u_seq_0101(

.clk (clk),

.rst_n (rst_n),

.seq_out (seq_out)

);

// 3. 生成时钟(5ns翻转,10ns周期)

always #5 clk = ~clk;

// 4. 仿真逻辑

initial begin

// 波形文件生成

$dumpfile("tb_seq_0101.vcd");

$dumpvars(0, tb_seq_0101); // 保存所有层级信号

// 控制台输出(ps单位,时间准确)

$monitor("Time=%0t ps: seq_out=%b", $time, seq_out);

// 激励流程:复位20ns → 持续输出0101…

rst_n = 1'b0;

#20; // 复位20ns(20000ps)

rst_n = 1'b1;

#180; // 运行180ns(总200ns=200000ps)

$finish;

end

endmodule

`endif // TB_SEQ_0101_V 保护块结束

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册