FPGA开发实战指南:从原理到项目应用

引言

在当今高速发展的数字时代,FPGA(Field-Programmable Gate Array,现场可编程门阵列)作为一种可重构的硬件平台,正日益受到工程师和研究人员的青睐。它以其独特的并行处理能力、高度的灵活性和快速的原型验证周期,在人工智能、数据中心、通信、图像处理等众多领域展现出巨大的应用潜力。对于希望深入硬件设计、追求极致性能的工程师而言,掌握FPGA开发技术已成为一项核心竞争力。

本文旨在为读者提供一份全面的FPGA开发实战指南,从最基础的原理出发,逐步深入到Verilog/SystemVerilog硬件描述语言、AXI总线协议、UVM验证方法学等核心技术,并结合实际项目应用,帮助读者构建完整的FPGA开发知识体系。无论您是初入FPGA领域的学生,还是寻求技术突破的资深工程师,本文都将为您提供有价值的参考和指导。

1. FPGA基础原理

FPGA的核心魅力在于其“可编程”的特性。与传统的固定功能芯片(如CPU、GPU)不同,FPGA允许用户通过编程来定义其内部的硬件逻辑功能。这得益于其独特的架构,主要由以下几个关键部分组成:

1.1 可编程逻辑单元 (CLB/LUT)

可编程逻辑单元(Configurable Logic Block, CLB)是FPGA的基本构建模块,其中最核心的组件是查找表(Look-Up Table, LUT)和触发器(Flip-Flop, FF)。

- 查找表 (LUT):LUT本质上是一个小型SRAM,用于实现任意组合逻辑功能。一个N输入的LUT可以实现2^N个输入变量的任意布尔函数。通过配置LUT中的SRAM单元,可以改变其输出与输入之间的逻辑关系。例如,一个4输入的LUT可以实现所有4输入组合逻辑功能。

- 触发器 (FF):触发器用于存储状态信息,是实现时序逻辑的关键。它们通常与LUT的输出相连,构成一个完整的时序逻辑单元。

1.2 可编程布线资源 (Routing Resources)

FPGA内部的CLB、I/O块、存储器等各种资源之间通过大量的可编程布线资源连接。这些布线资源包括长线、短线、专用时钟线等,通过配置开关矩阵(Switch Matrix)和连接块(Connection Block),可以实现任意逻辑单元之间的互联,从而构建复杂的数字电路。

1.3 嵌入式存储器 (Block RAM)

为了满足高性能应用对存储的需求,现代FPGA通常集成了大量的嵌入式存储器,通常称为Block RAM(BRAM)。这些BRAM可以配置为单端口RAM、双端口RAM、FIFO等多种模式,为数据缓存、查找表等应用提供高速存储解决方案。

1.4 数字信号处理单元 (DSP Slices)

随着FPGA在信号处理领域的广泛应用,许多FPGA芯片集成了专用的数字信号处理(DSP)单元,也称为DSP Slice。这些单元通常包含乘法器、加法器、累加器等硬件资源,能够高效地执行乘法累加(MAC)等DSP核心运算,显著提升FPGA在图像处理、通信算法等方面的性能。

2. Verilog/SystemVerilog硬件描述语言

Verilog和SystemVerilog是FPGA设计中最常用的硬件描述语言(HDL)。它们允许工程师以文本形式描述数字电路的行为和结构,并通过综合工具将其转换为FPGA可编程的比特流文件。

2.1 Verilog HDL基础

Verilog HDL是一种事件驱动、并发执行的语言,其核心概念包括:

- 模块 (Module):Verilog设计的最小单元,用于封装特定的硬件功能,具有输入、输出端口。

- 数据类型 (Data Types):如wire(线网)、reg(寄存器)、integer(整数)等,用于定义信号的类型和存储特性。

- 运算符 (Operators):包括算术运算符、逻辑运算符、位运算符等,用于描述数据操作。

- 行为描述 (Behavioral Description):使用always块、initial块等描述电路的时序行为。

- 结构描述 (Structural Description):通过实例化模块来描述电路的连接关系。

2.2 SystemVerilog的增强

SystemVerilog是Verilog的超集,在Verilog的基础上增加了许多强大的功能,使其更适合于复杂的SoC设计和验证,包括:

- 数据类型增强:引入了logic(四态逻辑)、enum(枚举类型)、struct(结构体)、union(联合体)等,提高了代码的可读性和可维护性。

- 接口 (Interface):提供了一种封装信号和协议的机制,简化了模块间的连接,并支持modport(端口模式)定义,增强了验证环境的构建能力。

- 类和面向对象编程 (Classes and OOP):引入了类、继承、多态等面向对象特性,极大地提升了验证环境的复用性和可扩展性,是UVM验证方法学的基础。

- 随机化 (Randomization):内置的随机化功能(rand、randc)使得生成多样化的测试激励变得简单高效。

- 覆盖率 (Coverage):提供了功能覆盖率(covergroup、coverpoint)和断言(assert)等机制,用于衡量验证的完备性。

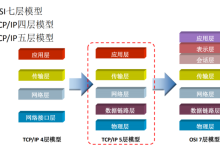

3. AXI总线协议

AXI(Advanced eXtensible Interface)是ARM公司提出的一种高性能、高带宽、低延迟的片上总线协议,广泛应用于SoC(System on Chip)和FPGA设计中,作为IP核之间以及处理器与外设之间互联的标准接口。理解AXI协议对于设计和集成复杂的FPGA系统至关重要。

3.1 AXI协议概述

AXI协议是AMBA(Advanced Microcontroller Bus Architecture)家族的一部分,主要特点包括:

- 分离的读写通道:读操作和写操作使用独立的地址和数据通道,可以并行进行,提高总线利用率。

- 多事务处理:支持乱序传输、突发传输,进一步提升数据吞吐量。

- 多主多从架构:允许多个主设备和从设备连接到同一总线,通过仲裁机制共享总线资源。

- 基于握手信号:所有通道都采用VALID/READY握手机制,确保数据传输的可靠性。

AXI协议主要包含五个独立的通道:

3.2 AXI-Lite与AXI4

AXI协议有多个版本,其中最常用的是AXI4和AXI-Lite:

- AXI4:全功能版本,支持高性能、高带宽的数据传输,适用于需要突发传输和复杂控制的场景。

- AXI-Lite:轻量级版本,简化了协议,不支持突发传输,主要用于寄存器访问和低带宽控制信号传输,例如配置IP核的控制寄存器。

4. UVM验证方法学

随着FPGA设计规模和复杂度的不断提升,传统的基于定向测试的验证方法已难以满足需求。UVM(Universal Verification Methodology,通用验证方法学)作为一种标准化的、基于SystemVerilog的验证方法学,为复杂的数字IC和FPGA验证提供了高效、可复用、可扩展的解决方案。

4.1 UVM核心概念

UVM基于面向对象编程(OOP)思想,其核心组件包括:

- 事务 (Transaction):抽象的数据包,代表一次总线操作或数据传输,是验证环境中的基本数据单元。

- 序列 (Sequence):用于生成一系列事务,模拟主设备的行为,是激励生成的核心。

- 序列器 (Sequencer):连接序列和驱动器,负责将序列生成的事务传递给驱动器。

- 驱动器 (Driver):将事务转换为底层总线信号,驱动DUT(Design Under Test,待验证设计)的输入端口。

- 监视器 (Monitor):从DUT的输出端口采集信号,将其转换为事务,供记分板和覆盖率模型使用。

- 记分板 (Scoreboard):用于比较DUT的输出与预期结果,判断设计功能是否正确。

- 代理 (Agent):封装了驱动器、监视器和序列器,代表DUT的一个接口。

- 环境 (Environment):集成多个代理、记分板、覆盖率模型等组件,构成完整的验证平台。

4.2 UVM的优势

- 可复用性:UVM组件(如Agent、Sequence)可以在不同的项目中复用,大大缩短验证周期。

- 可扩展性:基于OOP的特性,可以方便地扩展验证环境以适应新的设计需求。

- 随机化与覆盖率:结合SystemVerilog的随机化和功能覆盖率机制,实现高效的验证激励生成和验证完备性度量。

- 标准化:作为业界标准,UVM促进了验证IP的共享和团队协作。

5. FPGA项目实战:一个简单的AXI-Lite IP核设计与验证

为了更好地理解上述概念,我们以一个简单的AXI-Lite从设备IP核设计为例,展示FPGA开发的实战流程。该IP核包含一个可读写的32位寄存器,通过AXI-Lite总线接口进行访问。

5.1 IP核设计

首先,我们使用Verilog HDL设计AXI-Lite从设备IP核。核心逻辑包括AXI-Lite接口逻辑(AW/W/B/AR/R通道的握手信号处理)和一个内部寄存器。

// axi_lite_slave.v

module axi_lite_slave (

input wire ACLK,

input wire ARESETn,

// AXI4-Lite Write Address Channel

input wire AWVALID,

output wire AWREADY,

input wire [31:0] AWADDR,

// AXI4-Lite Write Data Channel

input wire WVALID,

output wire WREADY,

input wire [31:0] WDATA,

input wire [3:0] WSTRB,

// AXI4-Lite Write Response Channel

output wire BVALID,

input wire BREADY,

output wire [1:0] BRESP,

// AXI4-Lite Read Address Channel

input wire ARVALID,

output wire ARREADY,

input wire [31:0] ARADDR,

// AXI4-Lite Read Data Channel

output wire RVALID,

input wire RREADY,

output wire [31:0] RDATA,

output wire [1:0] RRESP

);

// Internal register

reg [31:0] my_register;

// AXI-Lite Write Logic

reg awready_reg;

reg wready_reg;

reg bvalid_reg;

reg [1:0] bresp_reg;

always @(posedge ACLK or negedge ARESETn) begin

if (!ARESETn) begin

awready_reg <= 1'b0;

wready_reg <= 1'b0;

bvalid_reg <= 1'b0;

bresp_reg <= 2'b00;

my_register <= 32'h0000_0000;

end else begin

// AWREADY

awready_reg <= AWVALID && !wready_reg && !bvalid_reg;

// WREADY

wready_reg <= WVALID && AWVALID && awready_reg;

// Write data to register

if (AWVALID && AWREADY && WVALID && WREADY) begin

if (AWADDR == 32'h0000_0000) begin // Example address

my_register <= WDATA;

end

end

// BVALID

bvalid_reg <= (AWVALID && AWREADY && WVALID && WREADY) || (bvalid_reg && !BREADY);

bresp_reg <= 2'b00; // OKAY

end

end

assign AWREADY = awready_reg;

assign WREADY = wready_reg;

assign BVALID = bvalid_reg;

assign BRESP = bresp_reg;

// AXI-Lite Read Logic

reg arready_reg;

reg rvalid_reg;

reg [31:0] rdata_reg;

reg [1:0] rresp_reg;

always @(posedge ACLK or negedge ARESETn) begin

if (!ARESETn) begin

arready_reg <= 1'b0;

rvalid_reg <= 1'b0;

rdata_reg <= 32'h0000_0000;

rresp_reg <= 2'b00;

end else begin

// ARREADY

arready_reg <= ARVALID && !rvalid_reg;

// RVALID

rvalid_reg <= (ARVALID && ARREADY) || (rvalid_reg && !RREADY);

// Read data from register

if (ARVALID && ARREADY) begin

if (ARADDR == 32'h0000_0000) begin // Example address

rdata_reg <= my_register;

end else begin

rdata_reg <= 32'hDEAD_BEEF; // Default for invalid address

end

end

bresp_reg <= 2'b00; // OKAY

end

end

assign ARREADY = arready_reg;

assign RVALID = rvalid_reg;

assign RDATA = rdata_reg;

assign RRESP = rresp_reg;

endmodule

5.2 UVM验证环境构建

为了验证上述AXI-Lite IP核的功能正确性,我们可以构建一个简单的UVM验证环境。这包括一个AXI-Lite Agent(包含Driver、Monitor、Sequencer)、一个Scoreboard以及一个Test Case。

- AXI-Lite Transaction:定义读写事务的数据结构。

- AXI-Lite Sequence:生成随机的读写事务。

- AXI-Lite Driver:将事务转换为AXI-Lite总线信号。

- AXI-Lite Monitor:捕获总线上的读写事务。

- Scoreboard:比较Monitor捕获的事务与预期模型。

- Test Case:实例化环境,运行序列,并检查结果。

为了更好地说明UVM中的事务(Transaction)概念,这里给出一个简化的AXI-Lite读写事务类定义示例:

// axi_lite_transaction.sv

class axi_lite_transaction extends uvm_sequence_item;

rand bit [31:0] addr;

rand bit [31:0] wdata;

rand bit [31:0] rdata;

rand bit is_write;

`uvm_object_utils_begin(axi_lite_transaction)

`uvm_field_int(addr, UVM_ALL_ON)

`uvm_field_int(wdata, UVM_ALL_ON)

`uvm_field_int(rdata, UVM_ALL_ON)

`uvm_field_int(is_write, UVM_ALL_ON)

`uvm_object_utils_end

function new(string name = "axi_lite_transaction");

super.new(name);

endfunction

// 可以在这里添加constrain来限制随机化范围

constraint addr_c { addr >= 32'h0000_0000; addr <= 32'h0000_00FF; };

endclass

这个axi_lite_transaction类定义了一个基本的AXI-Lite事务,包含地址、写入数据、读取数据以及一个指示读写操作的标志位。通过rand关键字,这些成员变量可以在UVM序列中被随机化,从而生成多样化的测试激励。uvm_object_utils宏用于注册类,使其能够被UVM框架识别和处理,例如进行拷贝、比较、打印等操作。在实际的验证环境中,还需要进一步实现序列、驱动器、监视器等组件来完整地验证DUT。

总结与展望

本文从FPGA的基础原理出发,详细介绍了Verilog/SystemVerilog硬件描述语言、AXI总线协议以及UVM验证方法学。通过一个简单的AXI-Lite IP核设计与验证示例,我们展示了FPGA开发从设计到验证的实战流程。FPGA技术以其独特的优势,在快速原型验证、高性能计算、边缘AI等领域持续发挥关键作用。随着半导体工艺的进步和设计工具的智能化,FPGA的开发门槛将进一步降低,应用场景也将更加广阔。

掌握FPGA开发不仅是掌握一项技术,更是培养一种并行思维和硬件抽象能力。希望本文能为您的FPGA学习之路提供坚实的基础和有益的启发。

更多精彩内容

如果您对数字IC设计、FPGA、Verilog、SystemVerilog、UVM、AXI总线等技术感兴趣,并希望通过生动的视频教程深入学习,欢迎关注B站UP主“bc宝懂一点IC”。这里有更多高质量的视频内容,助您在硬件开发的道路上不断前行!

B站搜索:bc宝懂一点IC(https://space.bilibili.com/492691141)

参考文献:

[1] CSDN博客. FPGA 学习系列(12):FPGA 应用开发与实现. https://blog.csdn.net/Azperk/article/details/146147946 [2] 野火. [野火]FPGA Verilog开发实战指南. https://doc.embedfire.com/fpga/altera/ep4ce10_pro/zh/latest/code/foreword.html [3] 知乎专栏. 手把手教你verilog实现AXI总线协议读写/FPGA. https://zhuanlan.zhihu.com/p/1188858143 [4] CSDN博客. System Verilog学习笔记(九)——验证环境结构. https://blog.csdn.net/ljy77882333/article/details/136299075 [5] EETOP论坛. FPGA应用开发实战技巧精粹华清远见培训资料完美清晰书签. https://bbs.eetop.cn/thread-613144-1-1.html [6] 吴鸿毅. Xilinx FPGA开发实用教程. http://wuhongyi.cn/FPGANote/pdf/XilinxISE/XilinxFPGA%E5%BC%80%E5%8F%91%E5%AE%9E%E7%B4%84%E6%95%99%E7%A8%8B%E7%AC%AC1%E7%89%88.pdf [7] Rockeric. UVM和C-完美结合. http://rockeric.com/2020/12/10/uvm%E5%92%8Cc-%E5%AE%8C%E7%BE%8E%E7%BB%93%E5%90%88/ [8] CSDN博客. 【经验分享】Xilinx AXI VIP使用说明. https://aijishu.com/a/1060000000359063 [9] CSDN博客. 15. 示例:创建AXI-Lite事务类(addr/data/rw)原创. https://blog.csdn.net/weixin_46163885/article/details/146043535 [10] CSDN博客. 精通技术写作:如何写出高质量技术文章?. https://blog.csdn.net/coder_heweilai/article/details/137756979 [11] CSDN博客. 技术文档写作风格指南. https://blog.csdn.net/katrina1rani/article/details/109443238 [12] CSDN博客. 12、技术内容写作规范与风格指南原创. https://blog.csdn.net/vim8coder/article/details/150141247 [13] 知乎专栏. 【全方位解析】如何写好技术文章. https://zhuanlan.zhihu.com/p/644639537

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册