AXI总线系统学习,这个总线是非常重要,很多地方都会要用,用到的话一定要好好学习

百度网盘链接:https://pan.baidu.com/s/1rDsLAXGj8WbX82teSkhuIw?pwd=1234 提取码: 1234

包含FPGA系统学习资料,免费分享

一、AXI总线 详细完整介绍(AMBA AXI)

1.1 AXI总线的基础定位

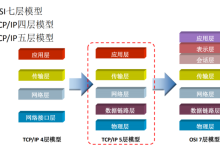

AXI(Advanced eXtensible Interface,高级可扩展接口)是ARM公司制定的AMBA总线协议簇中的核心成员,属于高性能片上互联总线(On-Chip Bus),主流版本为 AXI3 和 AXI4(目前FPGA/SoC中99%使用AXI4),是当前芯片内、异构芯片间数据交互的事实标准。

AXI总线设计的核心目标:高性能、高带宽、低延迟、高灵活性,专门解决片内多模块(CPU、FPGA逻辑、DDR、DMA、外设IP)之间的高速数据交互问题,也是FPGA开发中必须掌握的核心协议。

1.2 AXI总线的核心特性(灵魂,必掌握)

AXI能成为主流,核心源于其设计上的优秀特性,所有特性均为「提升传输效率、降低设计复杂度」服务,也是区别于AHB/APB等传统AMBA总线的关键:

- 发送方拉高VALID表示「数据/地址/响应有效,已准备好发送」;

- 接收方拉高READY表示「接收端就绪,可以接收数据」;

- 只有当 VALID & READY = 1 时,本次传输才算真正完成;

- 优势:完美解决总线拥塞、跨时钟域传输、模块速率不匹配的问题,抗干扰性极强。

1.3 AXI的核心架构:5个独立单向通道

AXI的所有数据交互,本质都是这5个单向通道的组合传输,所有通道均遵循READY-VALID握手机制,写事务用到3个通道,读事务用到2个通道,无任何交叉复用,这是AXI最核心的设计,必须牢记:

✅ 核心原则:所有通道都是「单向」的,要么是「主机→从机」,要么是「从机→主机」,没有双向信号线!

✔ 写事务(主机 → 从机,3个通道)

主机向从机写入数据的完整流程,依赖3个独立通道的协同,通道顺序可灵活,不强制严格先后:

✔ 读事务(主机 ← 从机,2个通道)

主机从从机读取数据的完整流程,依赖2个独立通道的协同:

1.4 AXI4的三大核心子集(FPGA开发 重中之重,必掌握)

完整版AXI4协议的信号线较多、逻辑复杂,但ARM在AXI4基础上,针对不同应用场景裁剪出了三个极简、高效的子集,这三个子集是 FPGA开发中唯一会用到的AXI形式(无例外),也是FPGA厂商官方IP核的标配接口,99%的FPGA工程只用到这三个子集,优先级:AXI4-Lite ≈ AXI4-Stream > AXI4,三者的定位、特性、应用场景严格区分,无兼容关系,但设计思想一致:

✅ 1. AXI4-Lite (轻量级AXI4,最常用)

- 核心定位:低速、轻量、寄存器级读写,是AXI4的最简裁剪版;

- 核心特性:只支持单拍传输(突发长度固定=1),地址必须32/64位对齐,数据位宽固定为32/64位,信号线极少(总共不到20根),实现难度为「零」;

- 核心应用场景:FPGA中所有外设IP的配置与控制,比如配置GPIO、SPI、I2C、UART、以太网的寄存器,读写片内控制寄存器等;

- FPGA地位:必备接口,所有FPGA官方IP核都提供AXI4-Lite接口,是FPGA逻辑与处理器(ARM/MicroBlaze)交互的核心桥梁。

✅ 2. AXI4 (标准AXI4,高性能)

- 核心定位:高速、大数据块传输,是完整版的AXI4协议;

- 核心特性:支持1~256拍突发传输,地址对齐,数据位宽支持32/64/128/256位等,信号线比AXI4-Lite多,实现难度中等;

- 核心应用场景:FPGA中高速数据交互,比如DDR3/DDR4读写、DMA数据搬移、高速外设(PCIe、SATA)的数据传输等;

- FPGA地位:高速数据场景必备,比如FPGA采集的海量数据写入DDR,或从DDR读取数据做实时处理。

✅ 3. AXI4-Stream (流式AXI4,FPGA第一高频接口,重中之重)

✨ 核心区别:AXI4-Stream 无地址线!无地址、无控制信息,只有纯数据流,是专门为「连续串行数据传输」设计的总线。

- 核心定位:高速、无地址、纯流式数据传输,是AXI4的「无地址版」,也叫AXIS;

- 核心特性:无地址、无突发限制,数据位宽任意(8/16/32/64/128位),核心握手机制为TVALID-TREADY,仅保留「数据有效+接收就绪」;可选信号:TLAST(帧结束标记,标记一包数据的末尾)、TUSER(用户自定义信号)、TKEEP(字节有效标记);

- 核心应用场景:FPGA中所有连续高速数据流场景,比如视频流(HDMI/DP)、ADC/DAC采集的模拟数据、以太网/光纤的数据包、PCIe的高速串行数据、DMA的数据流转发等;

- FPGA地位:绝对的第一高频接口,FPGA开发中80%的高速数据交互都是通过AXI4-Stream完成的,是FPGA的「生命线接口」。

二、FPGA如何实现AXI总线(完整落地指南,从入门到进阶)

✅ 前置核心结论(新手必看,避坑关键)

2.1 核心前提:AXI在FPGA中的角色

在FPGA中,AXI总线的角色是 「片内互联桥梁」:

- AXI主机(Master):发起数据传输的模块,比如FPGA的软核处理器(MicroBlaze)、硬核处理器(Zynq的ARM)、DMA控制器、自定义逻辑模块;

- AXI从机(Slave):接收并响应传输的模块,比如DDR IP、GPIO IP、SPI IP、以太网IP、自定义寄存器模块、ADC采集模块;

- 所有主机和从机,都通过AXI总线互联,实现数据的统一交互,一套总线适配所有模块,无需为不同外设设计不同的接口,大幅降低FPGA的设计复杂度。

2.2 思路一:调用官方IP核,零手写AXI协议逻辑(推荐,90%场景,新手首选)

✅ 核心优势

这是FPGA实现AXI总线的主流方式、最优方式、最高效方式,也是所有FPGA工程师的标配开发流程。官方AXI IP核已经由厂商做了极致优化:

- 内置完整的AXI协议逻辑、READY-VALID握手、时序约束、抗干扰处理;

- 经过严格的量产验证,稳定性100%,无协议bug;

- 图形化配置参数,无需手写任何AXI相关代码;

- 自动生成互联逻辑,一键完成模块间的AXI总线互联。

✅ 实现核心逻辑

FPGA开发AXI的本质:拼积木式开发 —— 把官方AXI IP核当作「积木」,用图形化工具把这些积木通过AXI总线连接起来,仅需编写少量逻辑完成「数据转发/寄存器配置」,即可实现完整的AXI总线功能。

✅ 具体实现步骤(通用流程,AMD/Intel均适用)

步骤1:新建FPGA工程,按需添加官方AXI IP核

根据需求选择对应的AXI IP核,比如:

- 做寄存器配置 → 添加 AXI GPIO/AXI SPI/AXI I2C IP(AXI4-Lite接口);

- 做高速数据存储 → 添加 AXI DDR3/DDR4 IP + AXI DMA IP(AXI4接口);

- 做高速数据流采集 → 添加 AXI ADC/DAC IP + AXI FIFO IP(AXI4-Stream接口)。

步骤2:图形化配置IP核参数

所有AXI IP核都支持图形化配置,比如:

- AXI4-Lite的GPIO IP:配置引脚数量、输入/输出模式;

- AXI4的DMA IP:配置数据位宽、突发长度、传输方向;

- AXI4-Stream的FIFO IP:配置数据位宽、深度、是否带TLAST信号。

步骤3:图形化互联AXI IP核(关键,零代码)

两大厂商均提供可视化的「块设计(Block Design)」工具:

- AMD/Xilinx:Vivado → Block Design;

- Intel/Altera:Quartus → Platform Designer (原Qsys);

在工具中,只需用鼠标拖拽,即可将不同IP核的AXI接口(如M_AXI主机接口、S_AXI从机接口)自动连接,工具会自动生成AXI互联IP(AXI Interconnect),完成地址映射、总线仲裁、数据路由,无需手写任何连线代码。

步骤4:生成HDL代码,编译下载

工具会根据图形化的互联关系,自动生成完整的HDL代码(Verilog/VHDL),直接编译即可下载到FPGA芯片中运行,全程零手写AXI协议逻辑。

✅ 入门实战案例(最经典,新手必做)

需求:通过AXI4-Lite控制FPGA的LED灯亮灭

✨ 这个案例的核心:你不需要懂任何AXI协议细节,只需要拼IP核,就能实现AXI总线的完整功能。

2.3 思路二:手动编写AXI接口适配逻辑(进阶,10%场景,定制化需求)

✅ 适用场景

当官方IP核无法满足定制化需求时,需要手动编写少量Verilog/VHDL代码实现AXI接口适配,比如:

✅ 核心原则(重中之重,避坑)

手动编写的核心是:只写「AXI接口适配层(Wrapper)」,不写完整的AXI协议栈!

- 我们只需要实现AXI的核心握手机制(READY/VALID) 和数据/地址的简单映射;

- 所有手动编写的AXI模块,都可以无缝对接官方AXI IP核,因为遵循相同的协议规则;

- 优先实现AXI4-Lite和AXI4-Stream,这两个是手动编写的高频场景,实现难度极低。

✅ 高频手动实现案例(附核心Verilog代码,直接可用)

案例1:手动实现「AXI4-Lite从机」(最易,入门必备)

需求:FPGA内部实现一个简单的AXI4-Lite从机,包含2个32位寄存器(地址0x00:控制寄存器,地址0x04:状态寄存器),主机可通过AXI4-Lite读写这两个寄存器。

核心逻辑:AXI4-Lite只支持单拍传输,只需处理AWADDR/AWVALID/AWREADY(写地址)、WVALID/WREADY/WDATA(写数据)、BVALID/BREADY/BRESP(写响应)、ARADDR/ARVALID/ARREADY(读地址)、RVALID/RREADY/RDATA/RRESP(读数据)的握手即可,无突发逻辑。

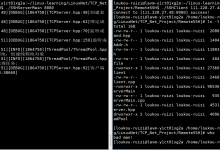

核心Verilog代码框架(关键逻辑,精简版)

// AXI4-Lite 从机核心逻辑 (32位地址/数据)

module axi4_lite_slave(

input clk,

input rst_n,

// 写地址通道

input [31:0] s_axi_awaddr,

input s_axi_awvalid,

output reg s_axi_awready,

// 写数据通道

input [31:0] s_axi_wdata,

input s_axi_wvalid,

output reg s_axi_wready,

// 写响应通道

output reg [1:0] s_axi_bresp,

output reg s_axi_bvalid,

input s_axi_bready,

// 读地址通道

input [31:0] s_axi_araddr,

input s_axi_arvalid,

output reg s_axi_arready,

// 读数据通道

output reg [31:0] s_axi_rdata,

output reg [1:0] s_axi_rresp,

output reg s_axi_rvalid,

input s_axi_rready

);

// 自定义寄存器:地址0x00=控制寄存器,0x04=状态寄存器

reg [31:0] ctrl_reg;

reg [31:0] stat_reg;

// 写事务:地址握手+数据握手+响应

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

s_axi_awready <= 1'b0;

s_axi_wready <= 1'b0;

s_axi_bvalid <= 1'b0;

ctrl_reg <= 32'd0;

end else begin

// 写地址就绪:当地址有效且数据未就绪时

if(s_axi_awvalid && !s_axi_awready) begin

s_axi_awready <= 1'b1;

end

// 写数据就绪:当地址已就绪且数据有效时

if(s_axi_wvalid && !s_axi_wready && s_axi_awready) begin

s_axi_wready <= 1'b1;

// 根据地址写寄存器

case(s_axi_awaddr)

32'h00000000: ctrl_reg <= s_axi_wdata;

32'h00000004: stat_reg <= s_axi_wdata;

default: ;

endcase

// 写响应有效

s_axi_bvalid <= 1'b1;

s_axi_bresp <= 2'b00; // 响应:成功

end

// 响应握手完成,清零就绪和有效信号

if(s_axi_bvalid && s_axi_bready) begin

s_axi_awready <= 1'b0;

s_axi_wready <= 1'b0;

s_axi_bvalid <= 1'b0;

end

end

end

// 读事务:地址握手+数据握手

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

s_axi_arready <= 1'b0;

s_axi_rvalid <= 1'b0;

s_axi_rdata <= 32'd0;

end else begin

// 读地址就绪:当地址有效且数据未就绪时

if(s_axi_arvalid && !s_axi_arready) begin

s_axi_arready <= 1'b1;

// 根据地址读寄存器

case(s_axi_araddr)

32'h00000000: s_axi_rdata <= ctrl_reg;

32'h00000004: s_axi_rdata <= stat_reg;

default: s_axi_rdata <= 32'h00000000;

endcase

// 读数据有效

s_axi_rvalid <= 1'b1;

s_axi_rresp <= 2'b00; // 响应:成功

end

// 读数据握手完成,清零就绪和有效信号

if(s_axi_rvalid && s_axi_rready) begin

s_axi_arready <= 1'b0;

s_axi_rvalid <= 1'b0;

end

end

end

endmodule

案例2:手动实现「AXI4-Stream数据转发」(FPGA第一高频,最简最实用)

需求:将一路AXI4-Stream输入数据流,无修改转发到一路输出数据流,核心是实现TVALID-TREADY握手和TDATA数据传输,可选TLAST帧结束标记。

核心特点:无地址、无控制,只有纯数据流,代码极简,是FPGA中最常写的逻辑之一。

核心Verilog代码(直接可用,完整版)

// AXI4-Stream 数据流转发模块 (64位数据位宽,带TLAST帧结束)

module axi4_stream_forward(

input clk,

input rst_n,

// AXI4-Stream 输入接口

input [63:0] s_axis_tdata,

input s_axis_tvalid,

output reg s_axis_tready,

input s_axis_tlast,

// AXI4-Stream 输出接口

output reg [63:0] m_axis_tdata,

output reg m_axis_tvalid,

input m_axis_tready,

output reg m_axis_tlast

);

// 核心逻辑:READY-VALID握手 + 数据透传

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

s_axis_tready <= 1'b0;

m_axis_tvalid <= 1'b0;

m_axis_tdata <= 64'd0;

m_axis_tlast <= 1'b0;

end else begin

// 接收就绪:当输出端就绪时,才允许输入端传输

s_axis_tready <= m_axis_tready;

// 输出有效:当输入端有效且接收就绪时

if(s_axis_tvalid && s_axis_tready) begin

m_axis_tvalid <= 1'b1;

m_axis_tdata <= s_axis_tdata;

m_axis_tlast <= s_axis_tlast;

end else begin

m_axis_tvalid <= 1'b0;

end

end

end

endmodule

2.4 FPGA实现AXI总线的关键设计要点(避坑指南,必看)

三、总结

✅ AXI总线核心总结

✅ FPGA实现AXI总线核心总结

AXI总线是FPGA开发的「必修课」,也是FPGA从入门到进阶的核心分水岭,掌握AXI总线后,就能轻松驾驭FPGA的高速数据交互、DDR读写、DMA传输等核心场景,也是做异构计算(FPGA+ARM)的必备技能。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册