SoC设计中的总线协议:AXI、AHB与APB的对比

摘要

在片上系统(SoC)设计中,各个IP核之间需要通过片上总线(On-Chip Bus)进行通信。ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)总线协议族是业界最广泛使用的片上互联标准,其中AXI、AHB和APB是最核心的三种协议。本文将深入对比这三种协议的特性、适用场景及其关键设计要点。

1. AMBA协议族概览

AMBA协议族经历了多个版本的演进,目前主流版本包括:

| AXI4 | Advanced eXtensible Interface 4 | 高性能、支持突发传输、读写通道分离 | 高带宽IP核(CPU、GPU、DMA) |

| AXI4-Lite | AXI4轻量版 | 简化版AXI,无突发传输 | 寄存器访问、低速控制接口 |

| AXI4-Stream | AXI4流式版 | 单向数据流,无地址通道 | 视频流、音频流、DSP数据流 |

| AHB | Advanced High-performance Bus | 中等性能,支持突发传输 | 中等带宽IP核(Flash控制器) |

| APB | Advanced Peripheral Bus | 低功耗、低带宽、简单接口 | 低速外设(UART、SPI、GPIO) |

2. AXI4协议详解

AXI4是AMBA协议族中性能最高的协议,其核心特性包括:

- 五个独立通道:写地址通道(AW)、写数据通道(W)、写响应通道(B)、读地址通道(AR)、读数据通道(R)。读写通道完全分离,支持全双工操作。

- Outstanding Transactions:主设备可以在收到前一个事务的响应之前,发出多个新的事务请求,极大地提高了总线利用率。

- 突发传输(Burst):支持最长256拍的突发传输,减少地址传输的开销。

- 握手机制(Handshake):每个通道使用VALID/READY握手信号,发送方置VALID表示数据有效,接收方置READY表示可以接收,两者同时为高时完成一次握手。

// AXI4写事务时序示意

ACLK : _|‾|_|‾|_|‾|_|‾|_|‾|_

AWVALID : _____|‾‾‾‾‾‾‾‾‾‾‾‾‾|___

AWREADY : _________|‾‾‾‾‾‾‾‾‾|___

// AWVALID & AWREADY同时为高 => 地址握手完成

3. AHB协议详解

AHB是一种共享总线协议,其特性包括:

- 流水线操作:地址相位和数据相位是流水线化的,即当前事务的数据相位与下一个事务的地址相位同时进行。

- 单一主设备:在任意时刻,只有一个主设备可以控制总线(通过仲裁器实现)。

- 突发传输:支持多种突发类型(SINGLE、INCR、WRAP)。

4. APB协议详解

APB是一种简单的非流水线协议,专为低功耗外设设计:

- 简单握手:使用PSEL、PENABLE、PWRITE等简单信号,无需复杂的握手机制。

- 两拍完成:一个APB事务通常在两个时钟周期内完成(Setup阶段和Access阶段)。

- 低功耗:由于接口简单,外设只需在PSEL有效时才激活,大部分时间处于低功耗状态。

5. 如何选择?

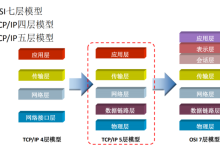

在SoC设计中,通常采用分层总线架构:高性能IP核(CPU、GPU)连接到AXI总线,中等性能IP核连接到AHB总线,低速外设连接到APB总线,层次之间通过桥接器(Bridge)相连。

结论

AXI、AHB和APB各有其设计目标和适用场景。理解这三种协议的特性,是进行SoC架构设计和IP核集成的基础。

欢迎关注我的个人网站:www.bcbao.club

更多IC设计与验证的干货、面试经验、学习资源,尽在其中!

B站: bc宝懂一点IC

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册