目录

-

- 一、目录结构

- 二、DC综合脚本

-

- 2.1 总脚本

- 2.2 脚本各部分详解

- 2.3 setupLib.tcl 文件详解

- 2.4 np2h0011_filelist.f 文件

- 2.5 adder.sdc 文件

- 2.6 rpt.tcl 文件详解

- 2.7 clean.sh文件

- 2.8 DC运行文件(run.sh)

- 三、补充

-

- 3.1 adder代码文件

- 3.2 nameRule.tcl脚本

- 3.3 compileOpt.tcl脚本

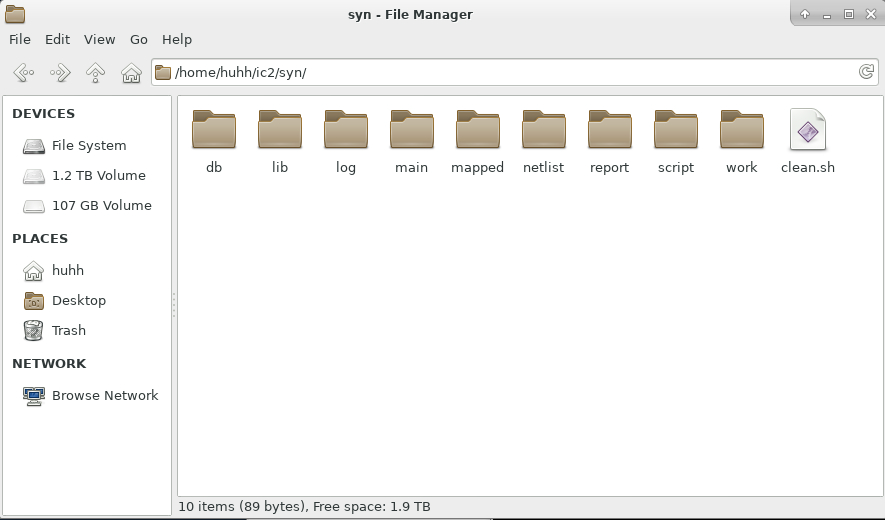

一、目录结构

可以看见,图中文件夹均在syn综合目录下。

可以看见,图中文件夹均在syn综合目录下。

各文件夹含义:

- db:存放Design Compiler的数据库文件(二进制的.ddc文件)

- lib:存放工艺库和IP库文件

- log:存放运行日志文件

- main:存放DC综合脚本np2h0011_syn.tcl(2.1)

- mapped:存放综合映射转换后的门级代码文件

- netlist:存放综合后生成的网表文件

- report:存放综合过程中产生的各种报告

- script:存放综合流程中调用的子脚本和配置文件

- work:工作区,存放运行脚本及中间文件

- clean.sh:清理脚本,用于清理前一次综合产生的所有文件

二、DC综合脚本

2.1 总脚本

#—————————————-

set view_name 20260130

set topDesign adder

set PROJECT np2h0011

set NETLIST_DIR ../netlist

set COMMON_DIR ../script

set rptPath ../report

set chkfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.check"]

set rptfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.rpt"]

set scrfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.scr"]

set vgfile [format "%s%s%s" "../netlist/" $PROJECT "_syn_${view_name}.vg"]

#/ read in lib & verilog files

#—————————————-

source $COMMON_DIR/setupLib.tcl

set_svf ../../fm/svf/syn_${view_name}.svf

suppress_message VER-130

suppress_message VER-936

suppress_message [list UID-401]

set hdlin_auto_save_templates true

sh rm -rf ./work/*

define_design_lib work -path work

analyze -library work -define { SYNTHESIS} -vcs { \\

+incdir+../.. \\

+incdir+../../rtl \\

} -format sverilog $COMMON_DIR/np2h0011_filelist.f

elaborate $topDesign

link

#/ link design

#—————————————-

current_design $topDesign

uniquify

check_design > ../report/check_design_${view_name}.rpt

#/ setting constrains

#—————————————-

#source -v -e $COMMON_DIR/set_dont_touch.tcl

#source -v -e $COMMON_DIR/clkCnst.tcl

#source -v -e $COMMON_DIR/groupPath.tcl

#source -v -e $COMMON_DIR/ioCnst.tcl

#source -v -e $COMMON_DIR/timeExcpt.tcl

#source -v -e $COMMON_DIR/drcCnst.tcl

source -v -e $COMMON_DIR/adder.sdc

#/ Compile design

#—————————————-

source -v -e $COMMON_DIR/nameRule.tcl

source -v -e $COMMON_DIR/compileOpt.tcl

check_timing > ../report/check_timing_${view_name}.txt

# clock gating

#————————

#compile -map_effort medium

set compile_enable_register_merging false

set_fix_multiple_port_nets -feedthroughs -buffer -all

current_design $topDesign

compile_ultra -no_autoungroup -no_seq_output_inversion -no_boundary_optimization -gate_clock -no_design_rule

#

#check_timing > 2.txt

#

#

#compile_ultra -no_autoungroup -no_seq_output_inversion -no_boundary_optimization -gate_clock -incr -no_design_rule

#write -f verilog -h -o ../netlist/$PROJECT.h.v

write -h -output ../db/compile_ultra.ddc

write -format verilog -hier -out ../mapped/design_net.v

#/ Report Design

#—————————————-

source $COMMON_DIR/nameRule.tcl

source $COMMON_DIR/rpt.tcl

set_svf off

# Exit

#—————————————-

exit

上述总脚本中涉及到关键的几个脚本为:

- setupLib.tcl:RTL代码的设计链接脚本

- np2h0011_filelist.f:文件列表(用于读取)

- adder.sdc:约束文件

- nameRule.tcl:命名规则

- compileOpt.tcl:编译优化选项设置脚本

- rpt.tcl:报告生成脚本

接下来会对上述几个重要脚本进行详细说明。

2.2 脚本各部分详解

- 1. 定义

# 变量定义

#—————————————-

# define variable for design

set view_name 20260130

set topDesign adder

# 路径和文件定义

set PROJECT np2h0011

set NETLIST_DIR ../netlist

set COMMON_DIR ../script

set rptPath ../report

# 输出文件路径定义(目录定义)

# 使用format命令格式化字符串生成文件名

set chkfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.check"]

# 生成格式:../report/np2h0011_syn_1226.check

# 作用:综合后设计检查文件

set rptfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.rpt"]

# 综合结果报告文件

set scrfile [format "%s%s%s" "../report/" $PROJECT "_syn_${view_name}.scr"]

# 脚本记录文件,可能包含综合过程中的命令

set vgfile [format "%s%s%s" "../netlist/" $PROJECT "_syn_${view_name}.vg"]

# 输出门级网表文件(.vg通常表示Verilog gate-level网表)

- 2. 设置

# 库文件设置

source $COMMON_DIR/setupLib.tcl

# SVF文件设置

set_svf ../../fm/svf/syn_${view_name}.svf

SVF文件记录综合过程中的所有设计变换,用于形式验证工具(如Formality)验证RTL与门级网表的一致性

- 3. 消息抑制

suppress_message VER-130

suppress_message VER-936

suppress_message [list UID-401]

-

作用: 抑制特定警告/信息

-

常用消息代码:

- VER-130:未使用的端口/信号

- VER-936:常量连接优化

- UID-401:设计保存相关信息

-

4. 优化操作

# 设置变量,在读取设计时自动保存设计模板

set hdlin_auto_save_templates true

# sh命令:执行shell命令

# 删除work目录下的所有文件,确保干净的编译环境

sh rm -rf ./work/*

# 定义一个名为"work"的设计库,路径为当前目录下的work文件夹

define_design_lib work -path work

- 5. 读取设计文件

analyze -library work -define { SYNTHESIS} -vcs { \\

+incdir+../.. \\

+incdir+../../rtl \\

} -format sverilog $COMMON_DIR/np2h0011_filelist.f

elaborate $topDesign

# 从RTL生成GTECH(通用技术)网表

link

# 解析设计中的所有模块、库引用

关键参数含义:

-

analyze:分析设计文件,建立中间表示

-

-library work:将分析结果存入work库

-

-define { SYNTHESIS}:定义SYNTHESIS宏,可用于RTL中的条件编译

-

-vcs:指定VCS风格选项

-

-format sverilog:指定SystemVerilog格式

-

$COMMON_DIR/np2h0011_filelist.f:文件列表文件,包含所有RTL文件路径

-

6. 设计检查和唯一化

current_design $topDesign

uniquify

check_design > ../report/check_design_${view_name}.rpt

- current_design:设置当前操作的设计

- uniquify:为每个实例创建唯一副本,解决重复实例问题

- check_design:检查设计基本问题

- 7. 约束加载

简略版:

source -v -e $COMMON_DIR/adder.sdc

.sdc文件直接包含了端口、时钟等约束

详细版本:

# -v: 详细模式,显示执行的命令

# -e: 出错时继续执行

source -v -e $COMMON_DIR/set_dont_touch.tcl

source -v -e $COMMON_DIR/clkCnst.tcl

source -v -e $COMMON_DIR/groupPath.tcl

source -v -e $COMMON_DIR/ioCnst.tcl

source -v -e $COMMON_DIR/timeExcpt.tcl

source -v -e $COMMON_DIR/drcCnst.tcl

- set_dont_touch.tcl:设置不优化的模块/实例

- clkCnst.tcl:时钟约束(频率、不确定性、延时等)

- groupPath.tcl:路径分组约束

- ioCnst.tcl:输入输出延时约束

- timeExcpt.tcl:时序例外(多周期路径、虚假路径等)

- drcCnst.tcl:设计规则约束(最大电容、转换时间等)

- 8. 规则设置

# 设置命名规则

source -v -e $COMMON_DIR/nameRule.tcl

# 编译优化选项

source -v -e $COMMON_DIR/compileOpt.tcl

# 检查时序约束的完整性和一致性

check_timing > ../report/check_timing_${view_name}.txt

set compile_enable_register_merging false

# 禁用寄存器合并优化

# 防止工具合并功能相同的寄存器,保持设计结构

set_fix_multiple_port_nets -feedthroughs -buffer -all

# 修复多端口网络问题

# -feedthroughs: 修复直通路径

# -buffer: 插入缓冲器

# -all: 修复所有多端口网络

- 9. 编译优化

# 重新设置当前设计,确保操作正确的设计

current_design $topDesign

compile_ultra -no_autoungroup -no_seq_output_inversion \\

-no_boundary_optimization -gate_clock \\

-no_design_rule

- -no_autoungroup:禁用自动取消层次结构

- -gate_clock:启用时钟门控优化

- -no_design_rule:不修复设计规则违规

- -no_seq_output_inversion:禁止触发器输出反相

- -no_boundary_optimization:禁止边界优化

- 10. 输出和报告

#write -f verilog -h -o ../netlist/$PROJECT.h.v

write -h -output ../db/compile_ultra.ddc

# 保存设计数据库

# -h: 保持层次结构

write -format verilog -hier -out ../mapped/design_net.v

# 输出Verilog门级网表(综合后)

# write命令:将当前设计以指定格式保存到文件中

source $COMMON_DIR/nameRule.tcl

# 重新加载命名规则,确保输出文件命名正确

source $COMMON_DIR/rpt.tcl

# 生成各种报告,通常包括:

# report_timing -nosplit

# report_area -nosplit

# report_power -nosplit

# report_constraint -nospli

set_svf off

# 停止记录SVF文件

# 避免影响后续操作

exit

# 退出Design Compiler

- 输出文件:

- DDC文件:二进制格式,包含完整设计信息

- 各种报告:时序、面积、功耗、违例等

DC中write命令通用语法:

write

[-format|-f] <format> # 输出格式

[-hierarchy|-hier|-h] # 保持层次结构

[-output|-o|-out] <filename> # 输出文件

[其他选项]

# 不指定-format时,根据文件扩展名自动判断

2.3 setupLib.tcl 文件详解

# STDCELL_LIBDIR:标准单元库目录,包含逻辑门、触发器等的时序库

set STDCELL_LIBDIR ../lib/arm_7t_rvt/db

# 将库文件添加到DC的搜索路径

set search_path [list $STDCELL_LIBDIR ]

# 设置DesignWare库路径(DesignWare库:Synopsys提供的可综合IP库)

set synthetic_library dw_foundation.sldb

#/* define db ( fst or tpl or slw ) */

#—————————————-

# 标准单元库配置(三个工艺角)

# 快速(FF)工艺角——延迟最小,用于保持时间(hold)分析

set STDCELL_LIBRARY_FAST [format "%s%s" $STDCELL_LIBDIR /sc7_logic018ll_base_rvt_ff_typ_min_1p98v_m40c.db]

# set STDCELL_LIBNAME_FAST ff_typ_min_1p98v_m40c

set STDCELL_LIBNAME_FAST sc7_logic018ll_base_rvt_ff_typ_min_1p98v_m40c

# 典型(TT)工艺角

set STDCELL_LIBRARY_TYPICAL [format "%s%s" $STDCELL_LIBDIR /sc7_logic018ll_base_rvt_tt_typ_max_1p80v_25c.db]

set STDCELL_LIBNAME_TYPICAL sc7_logic018ll_base_rvt_tt_typ_max_1p80v_25c

# tt:typical-typical,典型工艺角

# 1p80v:1.80V电压

# 25c:25°C温度

# typ_max:最大典型值

# 慢速(SS)工艺角——延迟最大,用于建立时间(setup)分析

set STDCELL_LIBRARY_SLOW [format "%s%s" $STDCELL_LIBDIR /sc7_logic018ll_base_rvt_ss_typ_max_1p62v_125c.db]

# set STDCELL_LIBNAME_SLOW ss_typ_max_1p62v_125c

set STDCELL_LIBNAME_SLOW sc7_logic018ll_base_rvt_ss_typ_max_1p62v_125c

# ss:slow-slow,最慢工艺角

# 1p62v:1.62V电压

# 125c:125°C温度

# typ_max:最大典型值

# 选择当前使用的工艺角(慢速角——设计将在最坏条件下进行综合)

set STDCELL_LIBRARY $STDCELL_LIBRARY_SLOW

set STDCELL_LIBNAME $STDCELL_LIBNAME_SLOW

# 目标库设置 [list …]创建列表,可包含多个库

set target_library [list $STDCELL_LIBRARY ]

# set link library 链接库设置

set link_library [list "*" $target_library ]

# *:已加载到内存中的设计

# $target_library:目标库(慢速标准单元库)

# $synthetic_library:DesignWare库

# $EFUSE_LIBRARY:EFUSE库

# 最小库设置

set_min_library $STDCELL_LIBRARY_SLOW -min_version $STDCELL_LIBRARY_FAST

# 主库:$STDCELL_LIBRARY_SLOW(慢速库,用于最大延迟)

# 最小库:$STDCELL_LIBRARY_FAST(快速库,用于最小延迟)

# 建立时间分析用慢速库(最大延迟)

# 保持时间分析用快速库(最小延迟)

#set_dont_use [find cell [format "%s%s" $STDCELL_LIBNAME "/*" ]]

2.4 np2h0011_filelist.f 文件

`include "rtl/adder.v"

此文件包含要被综合的所有RTL代码文件路径。

2.5 adder.sdc 文件

# adder.sdc

# 1. clock: 2ns (500MHz)

create_clock -name CLK -period 2.0 [get_ports clk]

# 2. clock_uncertainty

set_clock_uncertainty 0.1 [get_clocks CLK]

# 3. in/out

set_input_delay 0.8 -clock CLK [all_inputs]

set_output_delay 0.8 -clock CLK [all_outputs]

# 4. design rule

set_max_fanout 8 [current_design]

set_max_transition 0.2 [current_design]

# 5. env

set_load 0.05 [all_outputs]

包含一些简单约束,用于综合测试

2.6 rpt.tcl 文件详解

# 定义文件夹路径

set summary_dir "$rptPath/summary"

set analysis_dir "$rptPath/analysis"

set debug_dir "$rptPath/debug"

set config_dir "$rptPath/config"

# 创建文件夹

file mkdir $summary_dir

file mkdir $analysis_dir

file mkdir $debug_dir

file mkdir $config_dir

# Summary_dir (必读报告)

# 综合结果摘要

check_design -multiple_designs > $summary_dir/check_design_${view_name}.rpt

# 时序检查报告(未约束路径等时序问题)

check_timing > $summary_dir/check_timing_${view_name}.rpt

# 设计质量报告(时序、面积、功耗总结)

report_qor > $summary_dir/qor_${view_name}.rpt

# 约束违例报告(所有违例的简洁列表)

report_constraint -all_violators -nosplit \\

-max_delay \\

-multiport_net \\

-max_fanout \\

-max_capacitance \\

> $summary_dir/constraint_${view_name}.rpt

# 时序违例详情报告(负slack路径的详细信息)

report_timing \\

-attribute \\

-capacitance \\

-delay max \\

-enable_preset_clear_arcs \\

-input_pins \\

-slack_lesser_than 0 \\

-max_paths 5 \\

-nets \\

-nworst 2\\

-path full_clock \\

-transition > $summary_dir/timing_violate_${view_name}.rpt

# analysis_dir(深度分析目录)

# 建立时间时序报告(分析最差时序路径)

report_timing -delay max -max_paths 100 -nosplit -path full_clock_expanded -nets -transition_time -input_pins \\

> $analysis_dir/timing_max_${view_name}.rpt

# 面积报告(分析面积分布和优化)

report_area -hierarchy -physical -designware > $analysis_dir/area_${view_name}.rpt

# 功耗报告

report_power -nosplit > $analysis_dir/power_${view_name}.rpt

# 详细违例报告

report_constraint -all_violators -verbose \\

-max_delay \\

-multiport_net \\

-max_fanout \\

-max_capacitance \\

> $analysis_dir/constraint_${view_name}.rpt

# 零互连延迟分析(评估逻辑结构性能)

set_zero_interconnect_delay_mode true

report_timing -delay max -path full_clock_expanded -max_paths 10 -nets -transition_time -input_pins -nosplit \\

> $analysis_dir/zero_interconnect_timing_${view_name}.rpt

report_qor > $analysis_dir/zero_interconnect_qor_${view_name}.rpt

set_zero_interconnect_delay_mode false

# dubug_dir(特定问题分析目录)

# 高扇出网络

report_net_fanout -threshold 32 > $debug_dir/high_fanout_nets_${view_name}.rpt

# 时钟门控报告

report_clock_gating -multi_stage -verbose -gated -ungated \\

> $debug_dir/clock_gating_${view_name}.rpt

# 锁存器报告

query_objects -truncate 0 [all_registers -level_sensitive ] \\

> $debug_dir/latches_${view_name}.rpt

# 时钟树报告

report_clock_tree -summary -settings -structure \\

> $debug_dir/clock_tree_${view_name}.rpt

report_port -verbose -nosplit > $debug_dir/port_${view_name}.rpt

# 层次结构报告

report_hierarchy > $debug_dir/hierarchy_${view_name}.rpt

# 资源使用报告

report_resources -hierarchy > $debug_dir/resources_${view_name}.rpt

# config_dir(配置信息)

# 设计信息报告

report_design > $config_dir/design_${view_name}.rpt

# 时钟报告

report_clocks -attributes -skew > $config_dir/clocks_${view_name}.rpt

# 编译选项报告

report_compile_options > $config_dir/compile_options_${view_name}.rpt

# 隔离端口报告

report_isolate_ports -nosplit > $config_dir/isolate_ports_${view_name}.rpt

# Write Verilog

# —————————————————

# 命名规则修改

current_design $topDesign

change_name -rule verilog -h

define_name_rule gcore -restrict "\\\\\\[\\]"

define_name_rule gcore -remove_internal_net_bus

report_name_rule gcore

change_name -rule gcore -h

# 文件同步(确保文件系统写入完成)

sh sync

# DDC输出(应用命名规则后)

write -f ddc -h -output ../db/changename_${view_name}.ddc

# Verilog门级网表

write -f verilog -h -output ../netlist/${topDesign}_syn.vg

# SDC约束文件

write_sdc -nosplit -version 1.9 ../netlist/${topDesign}.sdc

# 最终DDC文件

write -h -f ddc -o ../db/${topDesign}_${view_name}.ddc

set_svf -off

脚本中未定义topDesign、view_name、rptPath等变量,是因为这些变量来自主综合脚本,通过source命令加载时,rpt.tcl继承主脚本的变量作用域。

2.7 clean.sh文件

rm db/* -rf

rm log/* -rf

rm netlist/* -rf

rm report/* -rf

rm mapped/* -rf

rm ../fm/svf/* -rf

每次综合前,需要运行此脚本清除上一次综合产生的各种文件,确保此次综合环境干净。

注意: 不要把script目录下的脚本文件全清理了!

2.8 DC运行文件(run.sh)

dc_shell -f ../main/np2h0011_syn.tcl |tee ../log/np2h0011_syn.log

此文件放置在work工作目录下,在work下直接运行此脚本即可(sh run.sh)

- dc_shell:启动DC(交互式命令行)

- dc_shell -gui:图形界面模式

- dc_shell-t:64位版本

- -f:指定脚本文件选项

- ../main/np2h0011_syn.tcl:综合脚本文件路径

- | :Linux管道符(重定向输出,将前命令输出作为后命令输入)

- tee:tee命令(无选项——覆盖文件)

- tee -a:追加到文件,而非覆盖

- tee -i:忽略中断信号

- ../log/np2h0011_syn.log:日志文件路径

三、补充

3.1 adder代码文件

module adder (

input clk,

input rst_n,

input [3:0] a,

input [3:0] b,

output reg [4:0] sum

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sum <= 5'b0;

end else begin

sum <= a + b;

end

end

endmodule

3.2 nameRule.tcl脚本

define_name_rules asic_top_rules -reset

define_name_rules verilog \\

-allow [list a-z 0-9 _] \\

-first_restrict [list 0-9 _] \\

-type net

define_name_rules verilog \\

-reserved [list always and assign begin \\

buf bufif0 bufif1 case casex casez cmos \\

deassign default defparam disable edge \\

else end endattribute endcase endfunction \\

endmodule endprimitive endspecify endtable \\

endtask event for force forever fork function \\

highz0 highz1 if initial inout input integer \\

join large macromodule medium module nand \\

negedge nmos nor not notif0 notif1 or output \\

parameter pmos posedge primitive pull0 \\

pull1 pullup pulldown reg rcmos reg release \\

repeat rnmos rpmos rtran rtranif0 rtranif1 \\

scalared small specify specparam strength \\

strong0 strong1 supply0 supply1 table task \\

time tran tranif0 tranif1 tri tri0 tri1 \\

trinand trior trireg use vectored wait wand \\

weak0 weak1 while wire wor xor xnor] \\

-target_bus_naming_style {%s[%d]}

#define_name_rules asic_top_rules -max_length 32 -type port

# Define core naming rule

# ———————–

define_name_rules asic_core_rules -reset

define_name_rules asic_core_rules -max_length 255

# Change name

# ———–

change_names -hierarchy -rules verilog

change_names -hierarchy -rules asic_core_rules

change_names -rules asic_top_rules

#——————————————————————–

# Set design write-out options

#——————————————————————–

set verilogout_no_tri true

3.3 compileOpt.tcl脚本

set verilogout_show_unconnected_pins "true"

set verilogout_no_tri "true"

set verilogout_single_bit "false"

# Compile Options

# ————————————————————

#/* we want to force it to use MUXes */

# ————————————————————

#set hdlin_dont_infer_mux_for_resource_sharing "false"

set hdlin_infer_mux false

# MISCELLANIOUS STUFF

# ————————————————————

set compile_no_new_cells_at_top_level true

set compile_instance_name_prefix "u"

set gen_max_ports_on_symbol_side 0

set bus_naming_style {%s[%d]}

#when use negedge,add inverter on clock and use posedge dff

# ————————————————————

set compile_automatic_clock_phase_inference none

current_design $topDesign

#

uniquify

set compile_seqmap_propagate_constants true

#set_boundary_optimization [find design "*"]

set_fix_multiple_port_nets -all -feedthroughs -outputs -buffer_constants

#set_flatten true -effort medium -minimize single_output -design [find design "*"]

set_structure true -timing true -design [find design "*"]

check_design

set_max_area 0

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册