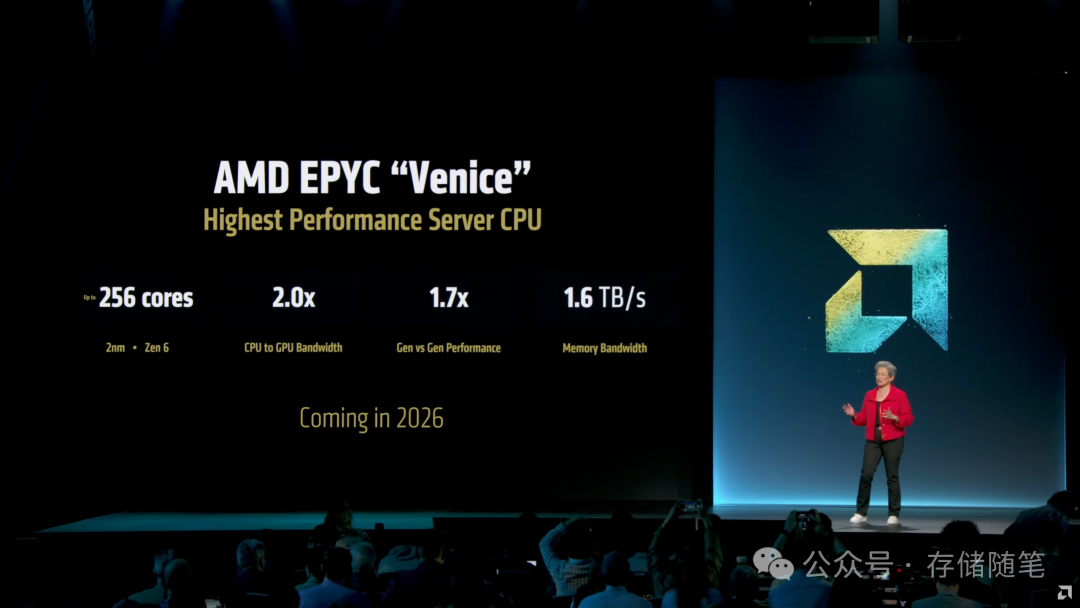

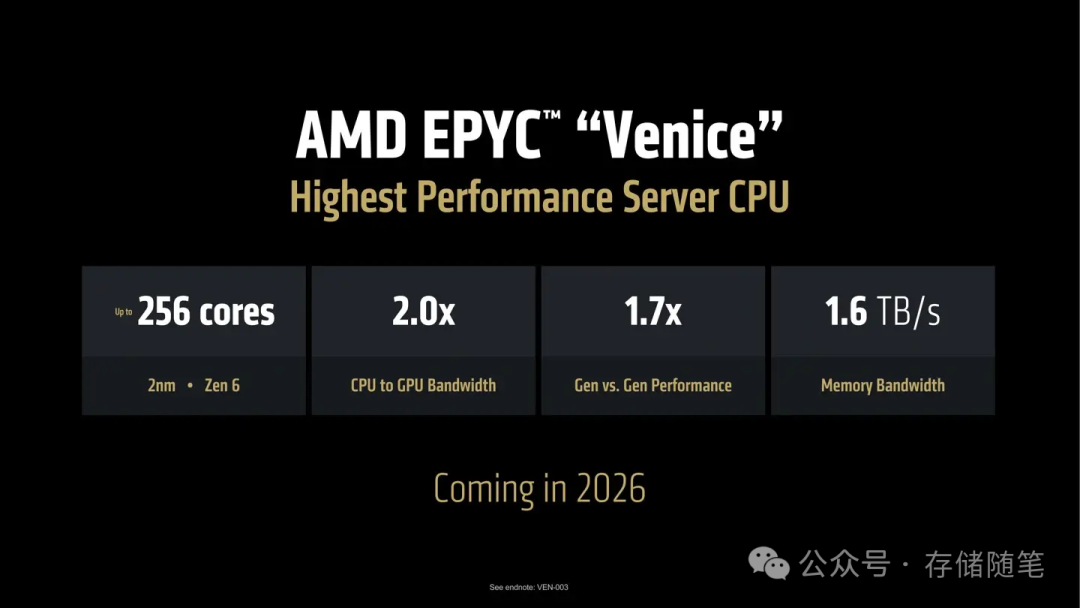

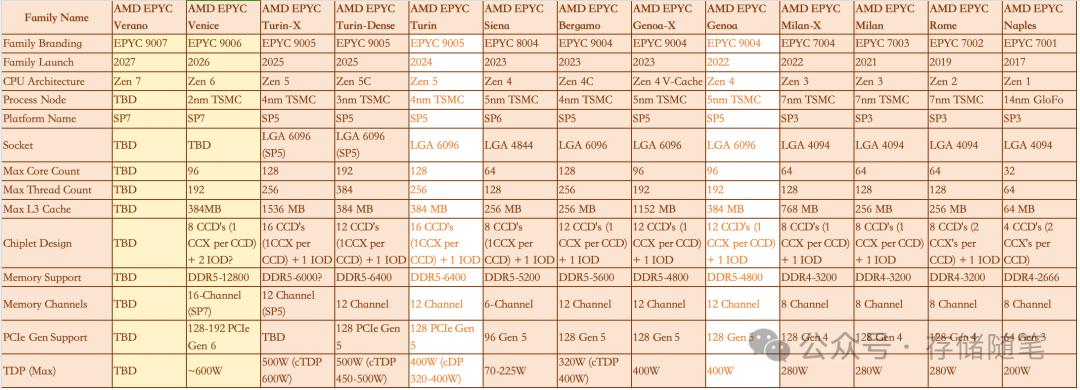

随着数据中心算力需求向\”核海战术\”演进,“AMD Advancing AI 2025”大会上披露第六代EPYC 9006 \”Venice\”处理器架构细节,揭示了x86服务器CPU的下一个技术奇点。这款基于Zen 6微架构的旗舰产品首次实现256核Zen 6c高密度核心配置,结合台积电2nm工艺与先进封装技术,正以\”算力密度革命\”回应英特尔Diamond Rapids等竞品的挑战。以下从架构创新、技术实现与市场影响三个维度展开深度解析。

一、双轨核心架构:Zen 6与Zen 6c

Venice系列最颠覆性的突破在于首次在同代产品中提供双核心架构选项,通过SP7/SP8双插座平台实现差异化算力覆盖:

1. Zen 6c高密度核心:256核的能效奇迹

-

核心布局:256核版本采用8个32核CCD(Compute Complex Die),每个CCD集成128MB L3缓存,整颗芯片L3缓存总量达1GB。这种设计相较Turin的192核Zen 5c实现33%核心数增长,且无需3D堆叠缓存(如3D V-Cache)即可达成超大容量缓存配置。

-

-

EPYC 9006 \”Venice\” With Zen 6C: 256 Cores / 512 Threads / Up To 8 CCDs

-

EPYC 9005 \”Turin\” With Zen 5C:192 Cores / 384 Threads / Up To 12 CCDs

-

EPYC 9006 \”Venice\” With Zen 5:96 Cores / 192 Threads / Up To 8 CCDs

-

EPYC 9005 \”Turin\” With Zen 5: 96 Cores / 192 Threads / Up To 16 CCDs

-

-

微架构特性:Zen 6c延续\”能效核心\”设计哲学,通过简化分支预测器、优化缓存层次结构,在保持每时钟周期指令数(IPC)基本不变的前提下,将核心面积压缩30%以上。台积电2nm工艺的引入进一步将漏电功耗降低40%,使256核CPU在600W TDP下仍能保持稳定运行。

-

应用场景:适用于云计算中的容器化部署、超大规模数据库分片、AI推理集群等对核心数敏感但单线程负载较轻的场景。例如,256核可同时运行超过1000个Docker容器,或支撑PB级数据仓库的并行查询。

2. Zen 6高性能核心:96核的极致算力

-

核心配置:标准Zen 6架构版本通过8个12核CCD实现96核设计,每个CCD搭载48MB L3缓存,总缓存容量384MB。相较Zen 5的8核CCD,单CCD核心数提升50%,L3缓存容量增加50%。

-

微架构进化:Zen 6将流水线深度从Zen 5的17级增至20级,配合全新分支预测器与动态指令调度单元,IPC提升约15%。同时引入AVX-512指令集支持(此前仅Intel独有),在科学计算、金融建模等浮点密集型任务中性能提升可达30%。

-

目标领域:聚焦HPC高性能计算、AI训练集群、实时数据分析等需要强单线程性能与高浮点算力的场景。例如,96核Zen 6可在气象模拟中缩短30%的预测时间,或在BERT模型训练中提升25%的吞吐量。

二、底层技术革新:从工艺到封装的全链路升级

1. 台积电2nm工艺:密度与能效的双重飞跃

-

晶体管技术:2nm工艺采用GAA(Gate-All-Around)环绕栅极晶体管,相较7nm FinFET工艺,晶体管密度提升约2倍,漏电电流降低70%。这使得Venice在相同Die面积下可集成更多核心,同时将每瓦性能提升50%。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册