跨越时钟鸿沟:异步FIFO在FPGA设计中的实战避坑指南

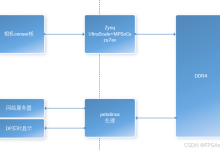

在现代高速数据采集系统中,FPGA开发者经常面临传感器低频时钟与处理器高频时钟之间的数据传输挑战。异步FIFO作为跨时钟域通信的核心组件,其稳定性和可靠性直接决定了整个系统的性能表现。本文将深入探讨异步FIFO在实际工程中的应用技巧,特别聚焦于那些容易被忽视却至关重要的设计细节。

1. 异步FIFO架构深度解析

异步FIFO的本质是一个双端口存储器,其读写操作分别由两个独立的时钟域控制。这种架构虽然解决了跨时钟域数据传输的基本需求,但也引入了潜在的时序风险。在实际设计中,我们需要特别关注指针同步机制和状态标志生成电路的工作原理。

读写指针的同步通常采用格雷码编码方式,这种编码方式的特点是相邻数值之间只有一位发生变化,能有效降低亚稳态传播的概率。但即使使用格雷码,仍然需要在目标时钟域中进行两级寄存器同步,这是确保信号稳定性的基本要求。

关键设计参数包括:

- FIFO深度计算:需综合考虑读写时钟频率差、数据突发长度和允许的最大延迟

- 存储介质选择:Block RAM、Distributed RAM或Built-in FIFO各有适用场景

- 状态标志设置:full/empty阈值的合理配置直接影响系统性能

注意:格雷码同步并不能完全消除亚稳态,但能将错误概率降到可接受的水平。在实际设计中,还需要考虑同步链的长度对时序的影响。

2. 复位策略与同步化处理

复位设计是异步FIFO中最容易被忽视却又至关重要的环节。许多工程问题都源于不恰当的复位处理方式,特别是异步复位信号的同步化问题。

Xilinx的xpm_fifo_async原语明确要求复位信号必须同步于写时钟域。这意味着直接使用异步复位信号连接到rst引脚将导致不可预知的行为。正确的做法是对异步复位信号进行同步化处理:

// 异步复位同步化示例

reg [2:0] rst_sync_ff;

always @(posedge wr_clk or posedge async_rst) begin

if (async_rst)

rst_sync_ff <= 3'b111;

else

rst_sync_ff <= {rst_sync_ff[1:0], 1'b0};

end

assign sync_rst = rst_sync_ff[2];

这种同步化处理确保了复位信号的释放与写时钟边沿对齐,避免了潜在的时序冲突。在实际工程中,我们还需要考虑复位解除后需要等待多少个时钟周期才能开始正常的读写操作。

复位验证步骤:

3. IP核配置关键参数详解

在选择和配置FIFO IP核时,多个关键参数的设置直接影响最终性能。Vivado中的FIFO Generator提供了丰富的配置选项,但需要根据具体应用场景进行合理选择。

接口类型选择:

- Native Interface:最基础的FIFO接口,提供直接的读写控制

- AXI4-Stream Interface:适合流式数据传输,支持背压机制

- AXI Memory Mapped:适用于内存映射访问场景

读模式配置:

- Standard Mode:读使能有效后下一个周期输出数据

- First-Word Fall-Through(FWFT):数据可用时立即输出,减少延迟

下表总结了关键配置参数的影响:

| FIFO深度 | 2的N次方 | 影响存储效率和资源使用 |

| 几乎满阈值 | 深度-2 | 避免写溢出,留出安全边际 |

| 几乎空阈值 | 2 | 确保及时响应读请求 |

| ECC使能 | 根据需求 | 增加可靠性但增加资源开销 |

在实际项目中,我们还需要注意读写数据宽度的匹配问题。当读写位宽不一致时,FIFO IP核会自动处理位宽转换,但这会引入额外的逻辑资源消耗。

4. 亚稳态规避与时序约束

跨时钟域设计无法完全避免亚稳态,但可以通过合理的工程设计将风险降到最低。除了使用格雷码和同步器外,还需要注意以下方面:

时序约束设置:

# 异步时钟域约束示例

set_clock_groups -asynchronous \\

-group [get_clocks wr_clk] \\

-group [get_clocks rd_clk]

这种约束告诉时序分析工具不要检查这两个时钟域之间的路径时序,避免产生不必要的时序违例报告。但需要注意的是,这并不意味着可以忽视实际的时序要求。

亚稳态防护措施:

- 使用同步器链处理所有跨时钟域信号

- 为异步信号设置适当的set_false_path约束

- 采用握手协议或异步FIFO处理大量数据传输

在实际调试中,ILA核是必不可少的工具。我们需要同时捕获读写时钟域的关键信号,包括数据、使能信号和状态标志,以便分析跨时钟域交互的实际情况。

5. 实战调试技巧与故障排查

基于实际项目经验,我们总结了一些常见的FIFO相关问题及其解决方案。这些问题往往在仿真阶段难以发现,只有在实际硬件环境中才会暴露。

常见问题1:写使能有效但数据无法写入

这种情况通常与复位信号同步化不足有关。建议检查:

- 复位信号是否满足rst引脚的电平要求

- 复位解除后是否等待了足够的时间再进行操作

- 写时钟域是否存在其他约束问题

常见问题2:空满标志异常

使用ILA同时捕获读写时钟域的以下信号:

// 监控信号列表

ila_inst ila (

.clk(wr_clk),

.probe0(wr_en),

.probe1(din),

.probe2(full),

.probe3(wr_data_count)

);

同时需要在读时钟域监控相应的读信号。通过对比分析两个时钟域的行为,可以快速定位问题根源。

性能优化建议:

- 在满足系统要求的前提下,尽量使用Block RAM资源

- 合理设置几乎满/几乎空阈值,避免频繁的状态切换

- 考虑使用独立时钟的分布式RAM实现小深度FIFO

6. 高级应用与性能优化

对于高性能应用场景,常规的FIFO配置可能无法满足要求。这时需要考虑一些高级优化技术。

流水线优化:

通过插入寄存器级来改善时序性能,虽然会增加少量延迟,但能显著提高最大工作频率。特别是在使用FWFT模式时,合理的流水线设计可以避免时序违例。

资源优化策略:

当设计中需要多个FIFO时,可以考虑使用可参数化的封装模块。例如基于xpm_fifo_async构建统一接口:

module custom_async_fifo #(

parameter DATA_W = 8,

parameter DEPTH_W = 8

)(

input wr_clk,

input rd_clk,

// … 其他接口信号

);

xpm_fifo_async #(

.FIFO_WRITE_DEPTH(2**DEPTH_W),

.READ_DATA_WIDTH(DATA_W),

.WRITE_DATA_WIDTH(DATA_W)

) fifo_inst (

// 端口连接

);

endmodule

这种封装不仅提高了代码的可重用性,还简化了多个FIFO实例的管理和验证工作。

在实际项目中,我们还需要关注功耗优化。不同的实现方式对动态功耗的影响很大,特别是在高速应用中。使用芯片内置的FIFO硬核通常比用逻辑资源实现的软FIFO更加节能。

经过多个项目的实践验证,这些设计方法和注意事项能够显著提高异步FIFO的可靠性和系统稳定性。每个项目都有其独特性,在实际应用中还需要根据具体需求进行调整和优化。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册