接前一篇文章:RTL8367RB芯片介绍(3)

七、引脚说明

2. 通用接口

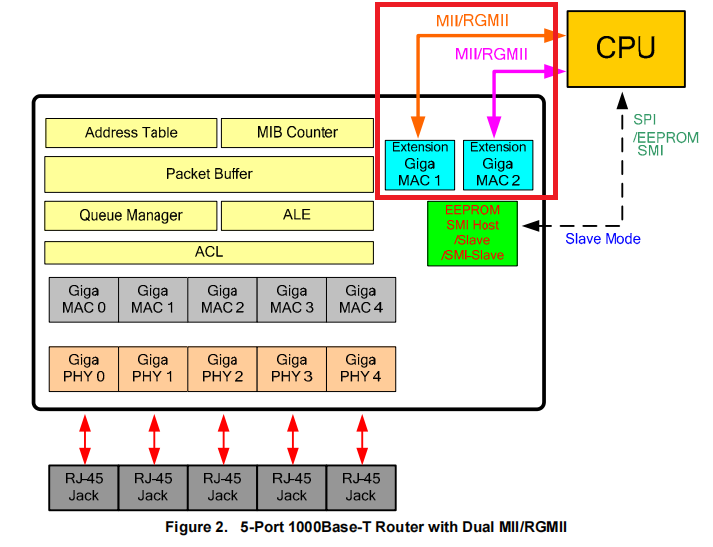

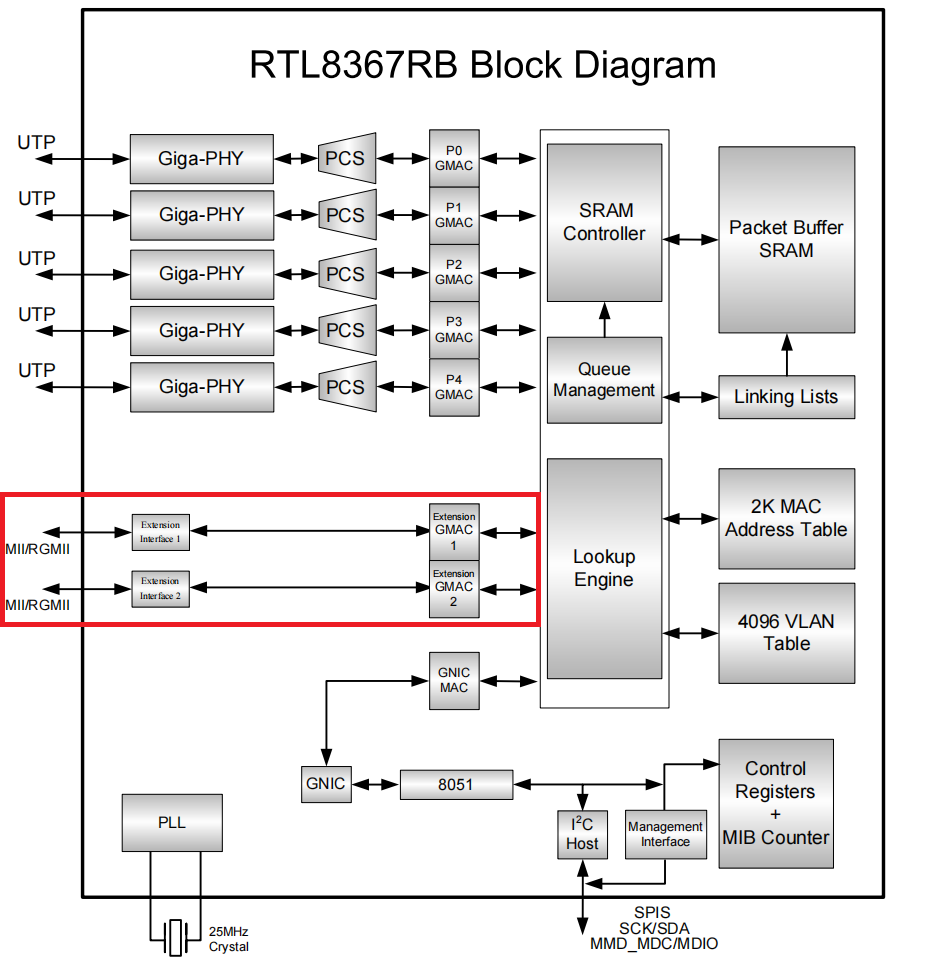

RTL8367RB支持多功能通用接口,可配置为MII/RGMII模式,用于扩展GMAC接口。RTL8367RB支持两个扩展接口(扩展GMAC0和扩展GMAC1),用于在特定应用中与外部PHY、MAC或CPU连接。这些扩展接口通过寄存器配置支持RGMII、MII MAC模式或MII PHY模式。

(1)RGMII引脚

RTL8367RB的扩展GMAC1和扩展GMAC2支持双RGMII接口,以便在寄存器配置设置为RGMII模式接口时与外部MAC或PHY设备连接。

扩展GMAC1 RGMII相关引脚如下表所示:

| RG1_TXD3 | 57 | O | – | RG1_TXD[3:0]扩展GMAC1 RGMII传输数据输出。 传输的数据同步发送到RG1_TXCLK。 |

| RG1_TXD2 | 58 | |||

| RG1_TXD1 | 59 | |||

| RG1_TXD0 | 60 | |||

|

RG1_TXCTL |

61 | O | – |

RG1_TXCTL扩展GMAC1 RGMII传输控制信号输出。 RG1_TXCTL在RG1_TXCLK的上升沿指示TX_EN,在RG1_TXCLK的下降沿指示TX_ER。 在RG1_TXCLK的下降沿,RG1_TXCTL=TX_EN(XOR)TX_ER。 |

| RG1_TXCLK | 62 | O | – |

RG1_TXCLK扩展GMAC1 RGMII传输时钟输出。 RG1_TXCLK为125MHz@1Gbps、25MHz@100Mbps和2.5MHz@10Mbps。 用于在RG1_TXCLK的上升沿和下降沿处同步RG1_TXD[3:0]和RG1_TXCTL。 |

|

RG1_RXCLK |

63 | I | – |

RG1_RXCLK扩展GMAC1 RGMII接收时钟输入。 RG1_RXCLK为125MHz@1Gbps、25MHz@100Mbps和2.5MHz@10Mbps。 用于在RG1_RXCLK上升沿和下降沿同步RG1_RXD[3:0]和RG1_RXCTL。 不使用时,必须用1K欧姆的电阻器将此引脚拉低。 |

| RG1_RXCTL | 64 | I | – |

RG1_RXCTL扩展GMAC1 RGMII接收控制信号输入。 RG1_RXCTL在RG1_RXCLK上升时指示RX_DV,在RG1_RX CLK下降沿指示RX_ER。 在RG1_RXCLK下降沿,RG1_RXCTL=RX_DV(XOR)RX_ER。 不使用时,必须用1K欧姆的电阻器将此引脚拉低。 |

|

RG1_RXD0 |

65 | I | – |

RG1_RXD[3:0]扩展GMAC1 RGMII接收数据输入。 接收到的数据由RG1_RXCLK同步接收。 不使用时,这些引脚必须用1K欧姆的电阻器拉低。 |

|

RG1_RXD1 |

66 | |||

|

RG1_RXD2 |

67 | |||

|

RG1_RXD3 |

68 |

扩展GMAC2 RGMII相关引脚如下表所示:

| RG2_TXD3 | 41 | O | – | RG2_TXD[3:0]扩展GMAC2 RGMII传输数据输出。 传输的数据同步发送到RG2_TXCLK。 |

| RG2_TXD2 | 42 | |||

| RG2_TXD1 | 43 | |||

| RG2_TXD0 | 44 | |||

|

RG2_TXCTL |

45 | O | – |

RG2_TXCTL扩展GMAC2 RGMII传输控制信号输出。 RG2_TXCTL在RG2_TXCLK的上升沿指示TX_EN,在RG2_TXCLK的下降沿指示TX_ER。 在RG2_TXCLK的下降沿,RG2_TXCTL=TX_EN(XOR)TX_ER。 |

| RG2_TXCLK | 46 | O | – |

RG2_TXCLK扩展GMAC2 RGMII传输时钟输出。 RG2_TXCLK为125MHz@1Gbps、25MHz@100Mbps和2.5MHz@10Mbps。 用于在RG2_TXCLK的上升沿和下降沿处同步RG2_TXD[3:0]和RG2_TXCTL。 |

|

RG2_RXCLK |

47 | I | – |

RG2_RXCLK扩展GMAC2 RGMII接收时钟输入。 RG2_RXCLK为125MHz@1Gbps、25MHz@100Mbps和2.5MHz@10Mbps。 用于在RG2_RXCLK上升沿和下降沿同步RG2_RXD[3:0]和RG2_RXCTL。 不使用时,必须用1K欧姆的电阻器将此引脚拉低。 |

| RG2_RXCTL | 48 | I | – |

RG2_RXCTL扩展GMAC1 RGMII接收控制信号输入。 RG2_RXCTL在RG2_RXCLK上升时指示RX_DV,在RG1_RX CLK下降沿指示RX_ER。 在RG2_RXCLK下降沿,RG2_RXCTL=RX_DV(XOR)RX_ER。 不使用时,必须用1K欧姆的电阻器将此引脚拉低。 |

| RG2_RXD0 | 49 | I | – |

RG2_RXD[3:0]扩展GMAC2 RGMII接收数据输入。 接收到的数据由RG2_RXCLK同步接收。 不使用时,这些引脚必须用1K欧姆的电阻器拉低。 |

| RG2_RXD1 | 50 | |||

| RG2_RXD2 | 51 | |||

|

RG2_RXD3 |

52 |

更多内容请看下回。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册