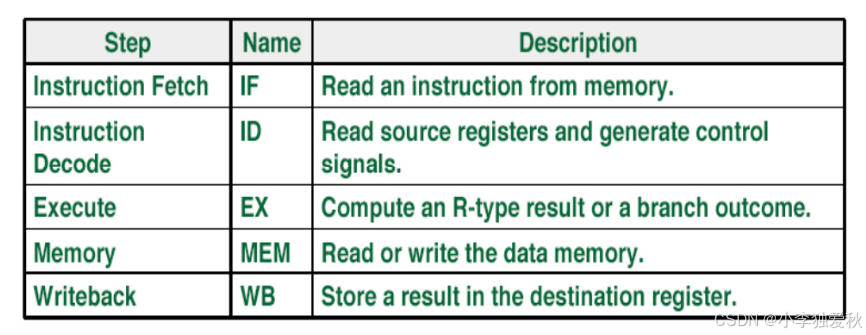

在MIPS处理器的多周期实现中,微指令作为控制单元的核心输出,直接驱动数据通路的协同运作。本文基于经典五级流水线理论(IF-ID-EX-MEM-WB),深入剖析五大类微指令的硬件行为与控制逻辑,并通过ADD指令的完整执行流程揭示其设计精髓。

一、微指令与数据通路的协同框架

微指令的本质是控制信号的时空组合,通过控制字段驱动以下关键硬件模块:

// 数据通路核心组件

PC模块 // 程序计数器

RegFile // 32×32位寄存器堆

ALU // 算术逻辑单元

MemUnit // 指令/数据存储器

MUX网络 // 多路选择器(控制数据流向)

📌 设计哲学:每条微指令控制一个时钟周期内的硬件动作,多周期CPU通过状态机串联微指令序列。

二、五大类微指令详解(附信号真值表)

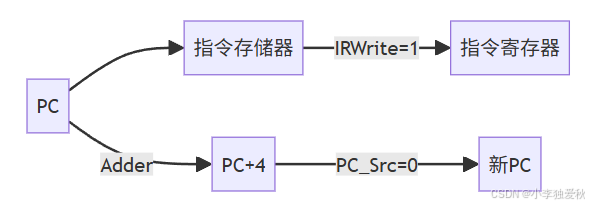

1. 取指微指令(IF)

硬件动作拓扑:

关键信号:

| MemRead | 1 | 启动指令存储器读操作 | 输出指令到总线 |

| IRWrite | 1 | 允许IR写入 | 锁存当前指令 |

| PC_Src | 0 | 选择PC+4路径 | PC←PC+4(顺序执行) |

💡 注:此阶段不依赖指令译码,为所有指令共享

2. 运算微指令(ALU Execution)

R型指令控制逻辑:

case(ALUOp)

2'b10: ALU_ctl = funct_field[3:0]; // 解析funct字段

default: // 其他操作码处理

endcase

信号组合:

| ALUSrcA | 1 | 选择RegA作为ALU输入1 |

| ALUSrcB | 00 | 选择RegB作为ALU输入2 |

| RegDst | 1 | 目标寄存器选择rd字段 |

| ALU_Result | – | 结果暂存于ALUOut寄存器 |

⚙️ 关键细节:funct字段在译码阶段已提取,本阶段映射为具体ALU操作

3. 访存微指令(Memory Access)

LW指令数据流:

基址寄存器 + 偏移量 → ALU计算地址 → Mem[addr] → MDR

信号组合:

| IorD | 1 | 选择ALU结果作内存地址 |

| MemRead | 1 | 启动数据存储器读操作 |

| MemtoReg | 1 | 标记结果需从内存加载 |

⚠️ 危险处理:存储器访问需2周期时插入stall信号

4. 分支微指令(Branch Control)

BEQ指令决策逻辑:

if (RegA == RegB)

PC = PC + (sign_ext(offset) << 2);

else

PC = PC + 4;

信号组合:

| ALUSrcB | 01 | 选择符号扩展立即数 |

| ALUOp | 01 | SUB比较(产生Zero标志) |

| PCSrc | 1 | 条件满足时选择分支地址 |

🔄 优化:现代MIPS通过分支预测减少流水线清空代价

5. 写回微指令(Write-Back)

双路径设计:

ALU结果 → RegFile (R型指令)

MDR → RegFile (LW指令)

信号组合:

| RegWrite | 1 | 1 | 允许写寄存器 |

| MemtoReg | 0 | 1 | 选择ALU/MDR数据源 |

| RegDst | 1 | 0 | 目标寄存器选择 |

三、ADD指令全流程:微指令的时空调度

以add $t1, $t2, $t3为例的硬件级执行时序:

| T1 | 取指(IF) | 读取指令 | PC→指令地址, IR←Mem[PC], PC←PC+4 | MemRead=1, IRWrite=1, PC_Src=0 |

| T2 | 译码(ID) | 读取t3 | RegFile读端口A←t2,读端口B←t3 | A_Write=1, B_Write=1 |

| T3 | 执行(EX) | ALU加法 | ALUOut←t2+t3 | ALUSrcA=1, ALUSrcB=00, ALUOp=10 |

| T4 | 写回(WB) | 结果存$t1 | Reg[$t1]←ALUOut | RegWrite=1, RegDst=1, MemtoReg=0 |

🔍 关键机制:

四、微指令设计的工程挑战与解决方案

1. 分支延迟槽问题

- 传统方案:分支指令后强制执行1条指令(延迟槽)

- 现代优化:采用动态分支预测器+投机执行,消除NOP浪费

// 分支预测示例

if (BranchPredictor.take_branch())

speculative_execute(target);

2. 控制信号冲突

当LW指令后紧接ADD指令时:

lw $t0, 0($sp)

add $t1, $t0, $t2 # $t0未就绪

解决方案:

- 硬件互锁:插入气泡(Stall)

- 编译器调度:重排指令序列

lw $t0, 0($sp)

nop // 硬件自动插入

add $t1, $t0, $t2

3. 原子操作支持

LL/SC指令对需要特殊微指令序列:

LL: // 加载链接

MemRead → LLbit置位

SC: // 条件存储

if (LLbit==1) 存储成功并清LLbit

else 存储失败

五、微程序 vs 硬布线:MIPS实现的权衡

| 性能 | 1指令≈4周期(多周期) | 1指令≈1周期(流水线) |

| 灵活性 | 可更新微码修复漏洞 | 需重新流片修改 |

| 设计复杂度 | 微程序ROM编码(易扩展) | 门级电路优化(高频设计) |

| 典型代表 | 教学用MIPS多周期CPU | MIPS R10000商用处理器 |

💎 结论:微程序控制以设计灵活性取胜,硬布线以峰值性能见长,现代CPU常采用混合方案

结语:微指令背后的体系结构思想

MIPS微指令设计体现了RISC架构的核心理念:

理解微指令的硬件映射关系,是掌握CPU设计精髓的关键。随着RISC-V等开源架构兴起,微程序思想仍在敏捷设计领域焕发新生。

网硕互联帮助中心

网硕互联帮助中心

评论前必须登录!

注册